# ATLAS実験アップグレード用 シリコン検出器テストシステムの開発および プロトタイプ検出器の性能評価

大阪大学大学院 理学研究科物理学専攻 山中卓研究室 博士前期課程2年

岡村航

平成23年3月1日

#### 概要

スイスのジュネーブ近郊にある欧州原子核研究機構 (CERN) で陽子・陽子衝突型 円形加速器である Large Hadron Collider (LHC) が稼働している。現在、LHC は重心系エネルギー7TeV で順調に物理データを収集している。LHC の衝突点の一つに汎用型粒子検出器である ATLAS 検出器があり、その内の一つにシリコンストリップ飛跡検出器である SemiConductor Tracker (SCT) がある。SCT はビーム衝突点近くに配置されているため、放射線損傷が激しい。2020 年前後に予定されている LHC のルミノシティアップグレード計画では O(1000fb<sup>-1</sup>) のデータ収集を想定している。このアップグレード後の高ルミノシティ下での運転のためには SCT の交換が不可欠であり、現在、そのプロトタイプの開発が精力的に進められている。本研究では、開発中の新型 SCT テスト用読み出しシステムを開発し、そこで得られた結果と既存の読み出しシステムを用いて得られたテスト結果とを比較し、開発した読み出しシステムが正しく動作している事を確認した。またプロトタイプの検出器の性能評価もこの読み出しシステムを用いて行うことができた。

# 目 次

| 第1章 | 序論・研究の背景                             | 6         |

|-----|--------------------------------------|-----------|

| 1.1 | LHC/ATLAS 検出器                        | 6         |

|     | 1.1.1 LHC (Large Hadron Collider)    | 6         |

|     | 1.1.2 ATLAS 検出器                      | 7         |

| 1.2 | SCT                                  | 8         |

| 1.3 | アップグレード用の新型 SCT                      | 9         |

| 1.4 | 本研究のねらい                              | 11        |

| 第2章 | シリコンストリップ検出器                         | <b>12</b> |

| 2.1 | 半導体検出器の一般論                           | 12        |

|     |                                      | 12        |

|     | 2.1.2 p型半導体とn型半導体                    | 13        |

|     |                                      | 14        |

|     |                                      | 14        |

| 2.2 |                                      | 17        |

| 2.3 | 放射線損傷                                | 19        |

| 第3章 | ABCN チップ                             | 22        |

| 3.1 | 各ブロックの説明                             | 22        |

|     | 3.1.1 Front-end                      | 23        |

|     | 3.1.2 Comparators                    | 24        |

|     | 3.1.3 Input Register & Mask Register | 24        |

|     |                                      | 25        |

|     |                                      | 25        |

|     | 3.1.6 Data Compression Logic         | 25        |

|     | 3.1.7 Readout Logic                  | 26        |

|     |                                      | 26        |

|     | 3.1.9 Command Decoder                | 27        |

|     |                                      | 27        |

| 3.2 | <u> </u>                             | 27        |

| 3.3 |                                      | 28        |

| 3.4  | チップの状態                     | 31        |

|------|----------------------------|-----------|

| 第4章  | 試験用読み出しシステム                | <b>32</b> |

| 4.1  | 汎用, 読み出し基板 SEABAS          | 32        |

|      | 4.1.1 SEABAS の仕様           | 33        |

|      | 4.1.2 読み出し用ファームウェア         | 34        |

| 4.2  | 読み出し用ソフトウェア                | 36        |

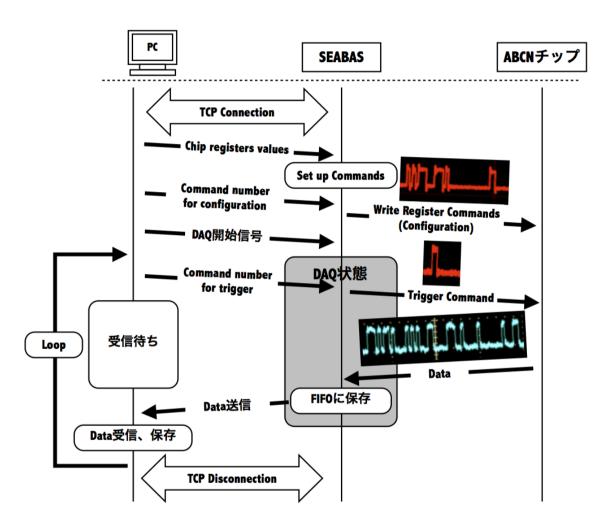

| 4.3  | DAQ の流れ                    | 37        |

| 4.4  | 読み出したデータの解析                | 37        |

| 4.5  | システムの動作確認                  | 39        |

|      | 4.5.1 1個の ABCN チップの読み出し    | 39        |

|      | 4.5.2 ハイブリッド基板の性能評価試験結果の比較 | 41        |

| 4.6  | DAQ システムの動作確認に関するまとめと考察    | 46        |

| 第5章  | プロトタイプ検出器の性能評価             | <b>50</b> |

| 5.1  | ノイズ測定                      | 51        |

|      | 5.1.1 バイアス電圧依存性            | 51        |

|      | 5.1.2 静電容量依存性              | 52        |

| 5.2  | 宇宙線による検出器効率の測定             | 55        |

|      | 5.2.1 セットアップ               | 55        |

|      | 5.2.2 トリガー                 | 55        |

|      | 5.2.3 閾値の設定                | 57        |

|      | 5.2.4 タイミング調整              | 58        |

|      | 5.2.5 検出効率測定               | 60        |

| 第6章  | まとめと考察                     | 63        |

| 第7章  | 結論                         | <b>65</b> |

| 付録 A | ABCN チップ                   | 66        |

| Λ 1  | データフォーマット                  | 66        |

# 図目次

| 1.1  | ATLAS 検出器                                  | 7  |

|------|--------------------------------------------|----|

| 1.2  | 内部飛跡検出器                                    | 7  |

| 1.3  | 内部飛跡検出器の断面図                                | 7  |

| 1.4  | バレル SCT モジュール                              | 8  |

| 1.5  | 新型 SCT モジュール                               | 10 |

| 2.1  | 絶縁体及び半導体中の電子のエネルギーのバンド構造                   | 12 |

| 2.2  | p 型半導体のバンド構造                               | 13 |

| 2.3  | n型半導体のバンド構造                                | 13 |

| 2.4  | p-n 接合による電荷分布                              | 14 |

| 2.5  | p-n 接合による電場の強さ                             | 14 |

| 2.6  | ・<br>逆バイアス電圧の印加                            | 15 |

| 2.7  | n バルク p <sup>+</sup> ストリップ型検出器             | 18 |

| 2.8  | p バルク n <sup>+</sup> ストリップ型検出器             | 18 |

| 2.9  | 放射線量に対しての不純物濃度と全空乏化電圧の変化                   | 19 |

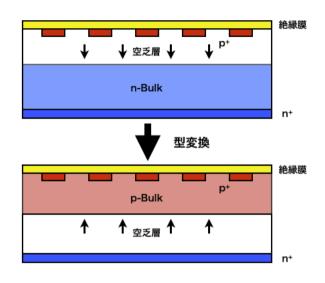

| 2.10 | 放射線損傷による型変換前後での現行 SCT の空乏化の様子              | 20 |

| 3.1  | ABCN チップのブロック図                             | 23 |

| 4.1  | SEABAS                                     | 32 |

| 4.2  | DAQ システムのブロック図                             | 35 |

| 4.3  | DAQのフローチャート (赤は送ったビットパターン、青は受け取った          |    |

|      | ビットパターン)                                   | 38 |

| 4.4  | "Clock Feed Through"から抜ける様子 (黄色がコマンド。青がチップ |    |

|      | からの出力。)                                    | 40 |

| 4.5  | "Send_ID Mode"でのL1トリガーコマンドに対するチップからの出力     |    |

|      | (黄色がコマンド。青がチップからの出力)                       | 40 |

| 4.6  | 各閾値に対してのノイズが閾値を越える回数の変化                    | 40 |

| 4.7  | Calibration パルス入力テスト                       | 41 |

| 4.8  | フレックスハイブリッド基板                              | 42 |

| 4.9  | strobe delay 試験                            | 42 |

| 4.10 | T DIES.                                    | 43 |

| 4.11       | Strobe delay 試験 (SCT DAQ)                                 | 44         |

|------------|-----------------------------------------------------------|------------|

| 4.12       | Calibration パルス入力タイミングに対する検出効率の依存性                        | 44         |

| 4.13       | 閾値毎の各チャンネルの検出効率 (SEABAS DAQ)                              | 45         |

| 4.14       | チャンネル 0 における検出効率の閾値依存性 (SEABAS DAQ)                       | 46         |

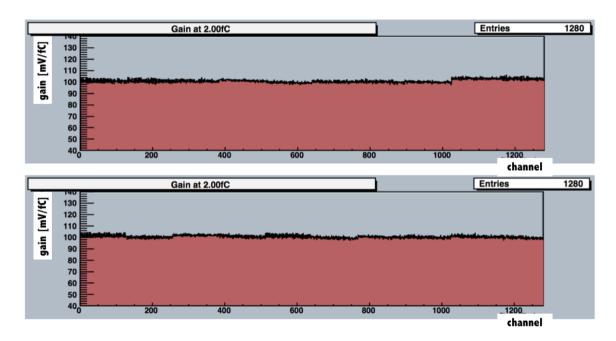

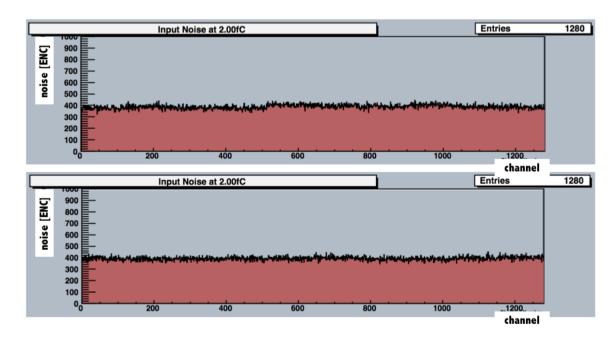

| 4.15       | SEABAS DAQ で測定した各チャンネルのゲイン [mV/fC] (上が link 0             |            |

|            | で下が link 1)                                               | 47         |

| 4.16       | SCT DAQ で測定した各チャンネルのゲイン [mV/fC] (上が link 0で               |            |

|            | 下が link 1)                                                | 47         |

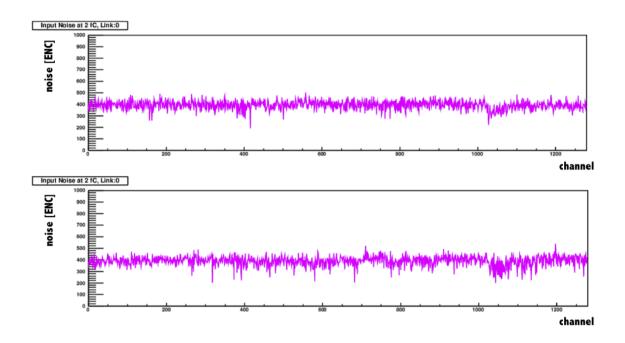

| 4.17       | SEABAS DAQ で測定した各チャンネルのノイズ [e] (上が link 0 で下              |            |

|            | が link 1)                                                 | 48         |

| 4.18       | SCT DAQ で測定した各チャンネルのノイズ $[e]$ (上が link $0$ で下が link $1$ ) | 48         |

| ۳ 1        | プロ l カノプ4〜II EE                                           | <b>F</b> 0 |

| 5.1        | プロトタイプ検出器・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             | 50         |

| 5.2        | センサー部の拡大図(水色がチップに接着されているセンサーであり、                          | <b>F</b> 0 |

| ۲ ،        | 白色はチップに接着されていないセンサーである)                                   | 50         |

| 5.3        | 逆バイアス電圧 [V] に対するノイズ [e] の変化 (chip 5 にはセンサーは<br>接着されていない。) | 52         |

| E 1        | <i>'</i>                                                  | 32         |

| 5.4        | センサーの静電容量 [pF] に対するノイズ [e] の変化 (静電容量が10.3 pF              | F 1        |

| <b>-</b> - | の時のノイズの値は chip 1 の方のノイズの値である)                             | 54         |

| 5.5        | 恒温槽内部のプロトタイプ検出器と3枚のシンチレータの配置の様子                           | 56         |

| 5.6        | センサーと3枚のシンチレータの配置を上から見た概略図                                | 56         |

| 5.7        | 各チャンネルのノイズが閾値を越える確率                                       | 57         |

| 5.8        | 各閾値に対しての Noise Occupancy の変化                              | 59         |

| 5.9        | 各閾値毎の各ストリップの検出効率 (実線は各チップに設定した閾値                          | co         |

| F 10       | $(Vt50+5\sigma))$                                         | 60         |

| 5.10       | エッジ検出"ON"の時のヒットパターン (XXX: Previous, Current, Next)        | 61         |

| 5.11       | エッジ検出"OFF"の時のヒットパターン (XXX: Previous, Current,             | 01         |

| F 10       | Next)                                                     | 61         |

| 5.12       | ヒットがあったイベントのストリップ分布                                       | 62         |

# 表目次

| 1.1 | LHC 加速器の主なデザインパラメータ                       | 6  |

|-----|-------------------------------------------|----|

| 1.2 | SCT のパラメータ                                | 8  |

| 1.3 | 新型のパラメータ                                  | 9  |

| 3.1 | データ圧縮の評価基準 (ここで X は'0' か'1' のどちらか)        | 26 |

| 3.2 | Calibration モード                           | 27 |

| 3.3 | ABCN チップ内部の主なレジスタのリスト                     | 28 |

| 3.4 | コマンドのフォーマット                               | 28 |

| 3.5 | Slow Control 用のコマンド                       | 29 |

| 5.1 | シリコンセンサーの主な仕様                             | 51 |

| 5.2 | 各チップに対する入力静電容量 [pF]                       | 53 |

| 5.3 | 3つのシンチレータのシングルレート                         | 56 |

| 5.4 | 各チップのセンサーの $Vt50[mV]$ と出力ノイズ $\sigma[mV]$ | 58 |

| A.1 | データフォーマット                                 | 66 |

| A.2 | ヒットデータフォーマット                              | 67 |

| A.3 | Isolated ヒットデータパケット                       | 67 |

| A.4 | Non Isolated ヒットデータパケット                   | 68 |

| A.5 | No Hit データパケット                            | 68 |

| A.6 | Configuration データパケット                     | 68 |

| A.7 | Register データパケット                          | 69 |

| A.8 | Read Register アドレス                        | 69 |

| A.9 | Error データフォーマット                           | 70 |

# 第1章 序論・研究の背景

この章では、LHC/ATLAS 検出器について簡単に紹介し、SCT、アップグレード 用の新型 SCT について述べた上で、本研究の目的を述べる。

# 1.1 LHC/ATLAS 検出器

# 1.1.1 LHC (Large Hadron Collider)

LHCはCERNにある陽子・陽子衝突型円形加速器である。LHCでは、質量の起源と考えられているヒッグス粒子の探索や、TeV領域での標準理論を超える新しい物理現象の探索、標準理論の精密測定など様々な研究が行われている。2009年11月に最初のビーム衝突に成功し、実験を開始した。現在は重心系エネルギー7TeVで順調に物理データを収集している。表1.1にLHC加速器の主なパラメータをまとめた。(ただし、これらの値は設計値であり、現在は達成されていない。)

LHC は 10 年間の運転で積分ルミノシティ700 fb<sup>-1</sup> のデータを収集する予定である。その後、ルミノシティを  $\sim 5 \times 10^{34}~\rm cm^{-2}s^{-1}$  にする Hight-Luminosity (HL) LHC が計画されている。HL-LHC は 2020 年頃から始まり、統計量は 3000 fb<sup>-1</sup> に達する予定である。

| 表 1.1: LHC 加速器の王なデサインパフメーク | :の王なアサインパフメーク | ソータ |

|----------------------------|---------------|-----|

|----------------------------|---------------|-----|

| 主リング周長         | 26.7 km                                 |

|----------------|-----------------------------------------|

| 重心系エネルギー       | 7  TeV + 7  TeV                         |

| ルミノシティ         | $10^{34} \text{ cm}^{-2} \text{s}^{-1}$ |

| 衝突頻度           | 40 MHz                                  |

| バンチ数           | 2808                                    |

| バンチあたりの陽子数     | $1.15 \times 10^{11}$                   |

| バンチ衝突当たりのイベント数 | 29 回                                    |

#### 1.1.2 ATLAS 検出器

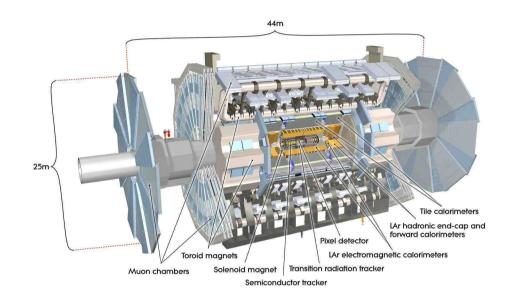

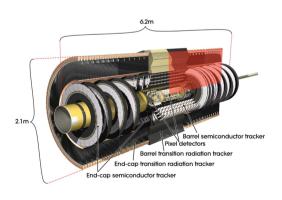

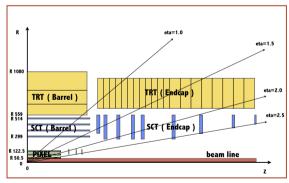

ATLAS 検出器は LHC の衝突点の一つに置かれた汎用粒子検出器である。図 1.1 に ATLAS 検出器の概観を示す。ATLAS 検出器は、外側からミューオン検出器、トロイダル磁石、ハドロンカロリメータ、電磁カロリメータ、ソレノイド磁石、内部飛跡検出器で構成されている。図 1.2 に内部飛跡検出器の概観を示す。内部飛跡検出器は、外側から Transition Radiation Tracker (TRT)、SCT、Pixel 検出器で構成されている。図 1.3 に図 1.2 の赤枠で示した部分の断面図を示す。内部飛跡検出器は、衝突点を原点とするビームラインからの極角を  $\theta$  とすると、擬ラピディティ $|\eta$  (=  $-\ln\tan(\theta/2)$ )| < 2.5 までを覆っている。

図 1.1: ATLAS 検出器

図 1.2: 内部飛跡検出器

図 1.3: 内部飛跡検出器の断面図

## 1.2 SCT

ここでは、ATLAS 検出器の内部飛跡検出器の1つである SCT について説明する。 SCT はバレル部に4 層、前後方部に各9 層から構成され、ビーム軸から 30 cm $\sim$ 52 cm の距離に配置される。SCT のパラメータを表1.2 にまとめる。

|                  | Barrel     | Endcap                       |

|------------------|------------|------------------------------|

|                  | (4 layers) | $(9 \text{ disks}) \times 2$ |

| module 数         | 2112       | 988×2                        |

| chip 数/module    | 6×2        | 6×2                          |

| channel 数/module | 768×2      | 768×2                        |

| 全 channel 数      | 324万       | 150万×2                       |

表 1.2: SCT のパラメータ

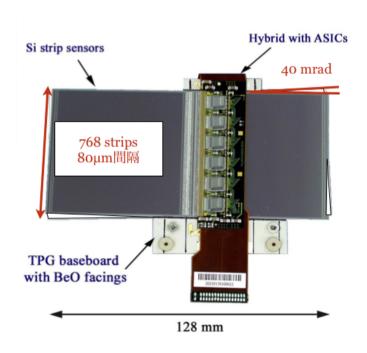

SCTのモジュールは、2枚一組のシリコンセンサーを 40 mrad の角度をつけてベースボードの裏表に接着し、読み出しチップを搭載したフレックスハイブリッド基板をのせたものから構成されている。図 1.4 にバレル SCT モジュールを示す。

図 1.4: バレル SCT モジュール

1 枚のシリコンセンサーは、 $6.4~{\rm cm} \times 6.4~{\rm cm}$  で、 $768~{\rm a}$  本の読み出しストリップが  $80~{\rm \mu m}$  の間隔で並んでいる。裏表のセンサーの読み出されたストリップの交点から

荷電粒子の入射位置を二次元的に検出する事ができる。センサーのストリップ間隔が 80 μm であることから、ストリップに垂直な方向では、

$$\frac{80\mu m}{\sqrt{12}} \simeq 23\mu m \tag{1.1}$$

以下の高精度で荷電粒子の入射位置を測定できる。

読み出しチップには放射線耐性に優れた ATLAS Binary Chip DMILL (ABCD) 3T チップを使用している [3]。ABCD3T チップはチップ当たり 128 チャンネルのストリップ信号を読み出すことができ、1 つのモジュールに裏表合わせて 12 個のチップが搭載されている。ABCD3T チップには ADC が搭載されておらず、ヒットがあったストリップの位置情報のみを読み出す。

LHC 実験ではビームの衝突点で、 $\sim 10^3$  の 1 MeV 以上の粒子が放出される。その結果、10 年間の運転で、SCT は  $\sim 2 \times 10^{14}/\mathrm{cm}^2$  の 1 MeV の中性子が通過するのと同等の放射線損傷を受け、飛跡検出器として要求される性能を満たさなくなる。そこで、現行の SCT はアップグレードで想定される数  $1000~\mathrm{fb}^{-1}$  のデータ収集に備え、 $\sim 2020$  年前後に放射線耐性に優れた新型 SCT と交換される。

# 1.3 アップグレード用の新型SCT

表 1.3 に新型 SCT のパラメータをまとめる。現行の SCT と比べると読み出しチャンネル数が大幅に増加する。

| module 数         | $\sim 7000$ |

|------------------|-------------|

| chip 数/module    | 40×2        |

| channel 数/module | 5120×2      |

| 全 channel 数      | ~7000万      |

表 1.3: 新型のパラメータ

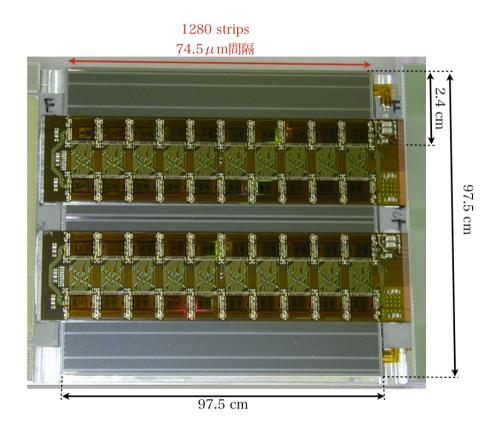

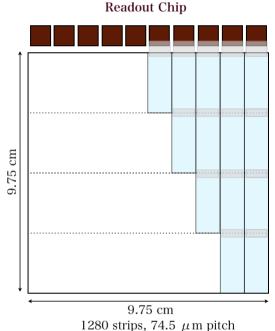

図 1.5 に現在開発中の新型 SCT モジュールを示す。読み出しチップを搭載したフレックスハイブリッド基板を 2 個のせたシリコンセンサーを、角度をつけて張り合わせたものからモジュールが構成されている。1 枚のシリコンセンサーは、9.75  $cm \times 9.75$  cm であり、1280 本の読み出しストリップが 74.5  $\mu m$  の間隔で備わっている。センサーはストリップの長さ方向に 2.4 cm ごとの 4 つのセグメントに分かれている。荷電粒子の通過位置の検出方法は現行の SCT モジュールと同様である。

HL-LHC でルミノシティを上げることによって、bunch crossing 当たりの事象数が30 (LHC) から150 (HL-LHC) に増加する。SCT では読み出しストリップ当たりの

図 1.5: 新型 SCT モジュール

Occupancy [/(events/readout)] を 1%以下にすることが要求されている [4]。その要求を満たすため、新型 SCT モジュールでは、読み出しチップ一つ当たりのシリコンセンサーのストリップ長を  $128~\mathrm{mm}$  から  $24~\mathrm{mm}$  へと短くしている。そのため、現在のSCT 領域をカバーするとなると、モジュール数が  $4088~\mathrm{mm}$  から  $\sim 7000~\mathrm{mm}$  に増加する。

読み出しチップには ABCD3T チップの発展型であり、より放射線耐性に優れた、ATLAS Binary Chip Next (ABCN) チップが使われる。ABCN チップは現在、IBM CMOS 250 nm 技術で実装されており、次世代のバージョンでは 130 nm 技術で実装される予定である。ABCN チップは 2.5~5 pF 程度の容量をもつシリコンストリップ検出器 (ストリップ長になおすと 2.5 cm 程度) に最適化されている。ABCN チップはチップ当たり 128 チャンネルのストリッ プ信号を読み出すことができ、1 つのモジュールに裏表合わせて 80 個搭載されている。ABCN チップも ABCD3T チップと同様で ADC が搭載されておらず、ストリップのヒット情報のみを読み出す。ABCN チップの詳細については第 3 章で説明する。

# 1.4 本研究のねらい

新型 SCT のための試験用読み出しシステムの開発が本研究の目的の一つである。試験用読み出しシステムは既に存在するが、読み出しハードウェアのバッファの容量と I/O の数の制限により、一度に 4 個のハイブリッド基板 (80 個の ABCN チップに相当)までしか読み出す事ができない。最終的には 4 個以上のモジュール (320 個以上の ABCN チップに相当)を読み出さなければならないため、既存の読み出しシステムでは不十分である。そこで大容量のバッファがあり多数の I/O を備えた読み出しシステムを構築し、将来 4 個のモジュールを読み出すための足がかりとして、複数個の ABCN チップを読み出す事が本研究のねらいである。また既存の読み出しシステムは高価で汎用性が低い。その問題を解消すべく安価で汎用性・利便性の高いシステムを開発する事も研究の目標である。

また開発した読み出しシステムを用い、新型 SCT 用プロトタイプモジュールの宇宙線に対する応答やノイズの定量的な評価をすることも本研究の目的の一つである。本論文の構成は以下のとおりである。

第2章で半導体検出器の一般論とシリコンストリップ検出器の動作原理について、第3章で新型SCTに搭載されている読み出し用ASICチップについて、第4章で開発したテスト用読み出しシステムについて、第5章でプロトタイプの検出器の性能評価について述べた上で、第6章でまとめと考察を述べる。最後に第7章で結論を述べる。

# 第2章 シリコンストリップ検出器

この章ではまず半導体検出器の一般論について述べ、その後シリコンストリップ 検出器について説明する。

# 2.1 半導体検出器の一般論

#### 2.1.1 半導体

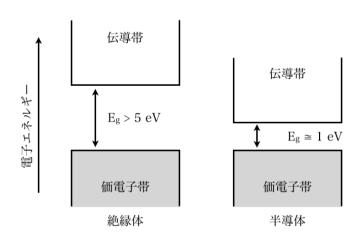

絶縁体あるいは半導体のバンド構造を図2.1 に示す。下側のバンドは価電子帯と呼ばれ、結晶中の特定の格子位置に束縛されている外殻電子に対応する。シリコンの場合、この電子は共有結合の一部になっている。上側のバンドは伝導帯と呼ばれ、結晶中を自由に移動する電子に対応している。このバンド内の電子が物質の電気伝導に寄与する。価電子帯と伝導帯はバンドギャップで分離されている。バンドギャップのエネルギー幅をEgと呼ぶ。温度がゼロでない場合、結晶中の電子は熱エネルギー

図 2.1: 絶縁体及び半導体中の電子のエネルギーのバンド構造

を持っているので、価電子帯に存在している電子は伝導帯へ熱励起しうる。この励起過程は伝導帯中に電子を1個作るだけではなく、電子が完全に詰まっていた価電子帯中に穴、すなわち正孔を1個作る。電子と正孔の両者の移動が物質中の電気伝導をもたらす。

絶縁体の Eg は 5 eV あるいはそれ以上であるのに対して、半導体の Eg は ~1 eV である。バンドギャップの大きさで、その物質が半導体あるいは絶縁体であるかが決まり、純粋なシリコンは熱励起により伝導体へ励起した電子が存在することにより、多少の伝導性を示すため、半導体である。導体では、価電子帯と伝導帯が重なっているため常に高い伝導性を示す。

### 2.1.2 p型半導体とn型半導体

4価のシリコン結晶中にホウ素などの3価の元素の不純物を注入すると、結晶中の共有結合に使われる電子が一つ足りなくなる。この電子の足りない穴が正孔として振る舞う。この時の不純物をアクセプターと呼ぶ。正孔を埋める電子は特定の場所に束縛されているが、通常の価電子ほど強くは束縛されていない。アクセプターからのこの極めてゆるく束縛されている電子はバンドギャップ内にエネルギー準位(アクセプター準位)をつくる。この時のバンド構造を図2.2に示す。アクセプター準位と価電子帯の間のエネルギー間隔は小さい(シリコンの場合、~0.05 eV)ため、常温で価電子帯の電子がこの準位に遷移することができる。そのため、遷移した電子の後にあいた穴が、電気伝導をもたらす自由な正孔として振る舞う。これがp型半導体である。

一方、シリコン結晶にリンなど 5 価の元素を不純物として注入すると、共有結合に参加せずに余る電子ができる。この時の不純物をドナーと呼ばれる。ドナーからの余分な電子はバンドギャップ内にエネルギー準位 (ドナー準位) をつくる。この時のバンド構造を図 2.3 に示す。ドナー準位と伝導体の間のエネルギー間隔は小さい (シリコンの場合、 $\sim 0.05$  eV) ため、常温でドナー準位の電子が価電子帯に遷移することができる。そのため、遷移した電子が電気伝導をもたらす自由な電子として振る舞う。これが n 型半導体である。

一般的には半導体の不純物の濃度は、シリコンの密度が $O(10^{22} \text{ atoms/cm}^3)$  に対して、 $O(10^{13} \text{ atoms/cm}^2)$  である。これに対して、不純物の濃度が非常に大きく $O(10^{20} \text{ atoms/cm}^2)$  になる p 型、n 型半導体はそれぞれ特に"+"をつけて、p<sup>+</sup> 型半導体、n<sup>+</sup> 半導体と呼ぶ。

図 2.2: p型半導体のバンド構造

図 2.3: n型半導体のバンド構造

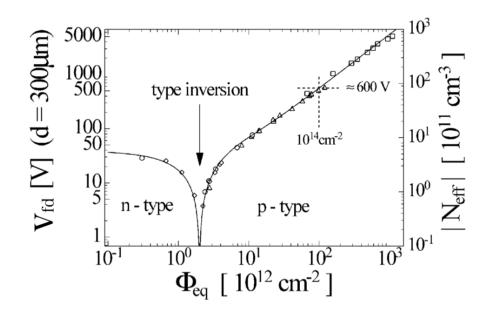

#### 2.1.3 ダイオード型半導体検出器の基本特性

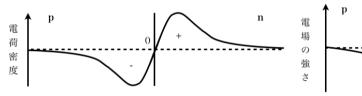

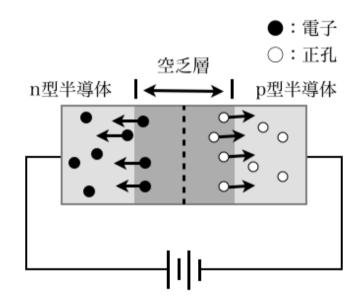

一般的に用いられている半導体検出器は、ダイオード型半導体であり、p型半導体とn型半導体を接合 (p-n接合)した構造をもつ。p-n接合部分では、電子濃度あるいは正孔濃度が異なるために、それぞれの領域の電子と正孔が他の領域に向かって拡散していく。p型半導体ではn型から拡散された電子が正孔と再結合し、n型半導体ではp型から拡散された正孔が電子と再結合する。その結果、電気的に中性であったp型半導体及びn型半導体は、この正孔と電子の再結合により、n型半導体には正電荷が、p型半導体には負電荷が余分に存在することになる。この電荷により p-n接合を横切る電場が形成され、平衡状態では電子と正孔の拡散が止まり、定常状態の電荷分布が確立される。この電荷分布を図 2.4 に、電場を図 2.5 に示す。この電荷分布により、p-n接合の両側には p型および n型半導体の不純物濃度によって決まる電位差が生じる。この電位差を p-n接合電圧といい、一般的には ~1 V である。

図 2.4: p-n 接合による電荷分布

図 2.5: p-n 接合による電場の強さ

p-n 接合部分は、電子と正孔が再結合しているので自由な電荷が存在せず、空乏層領域と呼ばれる。この領域に荷電粒子などが入射してきて、エネルギーを価電子帯の電子に与えると、この電子は伝導帯に遷移しその跡に正孔ができる。この電子と正孔は、空乏層領域に電荷がないことから再結合できず、この領域の電場のためそれぞれのnとp領域に引き寄せられる。一対の電子正孔対を作るために必要なエネルギーはシリコンの場合、3.6 eV であるので、運ばれてきた電荷量を測定することによって、空乏層領域に与えられたエネルギーが分かる。

## 2.1.4 逆バイアス電圧の印加

ここまで外部電圧を印加していない半導体ダイオード型検出器について議論してきた。このような検出器では、検出器として動作はするが十分な性能は示さない。上で述べたように p-n 接合電圧は約1 V である。この電位差での電場では、作られた電子や正孔を高速に電極に収集できない。また空乏層領域の厚さが数  $\mu m$  程度と非常に薄いため、空乏層領域で荷電粒子が落とすエネルギーが少なく、実用には向かない。さらに、その外側には空乏化されていない領域が広がっており、空乏層で作

られた電子や正孔がこの領域の正孔や電子と再結合して、外部に電気信号を出力しない可能性がある。

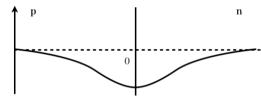

以上の問題はp-n接合部にp側よりもn側の電位が高くなるように外部電圧 (逆バイアス電圧) を印加することによって解決できる (図 2.6)。空乏領域は自由な電荷が存在しないことから、電気抵抗が非常に高い状態である。そのため p-n 接合に逆バイアス電圧を印加した場合、逆バイアス電圧はすべて空乏層にかかる。逆バイアス電圧は、p-n接合にかかる電位差を強める。その結果、空乏層の厚さが増大し、入射粒子が作った電子正孔対を集めうる体積が拡大する。十分な逆バイアス電圧を印加することにより、検出器全体を空乏化することも可能である。これを全空乏化といい、その時の逆バイアス電圧を全変乏化電圧と呼ぶ。検出器全体が全空乏化されれば、入射粒子が生成した電子正孔対は再結合して失われてしまうこと無くそれぞれの電極に到達し、検出器外部に電気信号をもたらす。検出器を全空乏化することは入射粒子により生成された電荷の収集効率をあげるために重要である。

図 2.6: 逆バイアス電圧の印加

ここで、簡単に逆バイアス電圧を加えたときの p-n 接合の性質を考えてみる。いま p-n 接合された検出器の電荷分布  $\rho(x)$  が、理想的に

$$\rho(x) = \begin{cases} eN_D & (0 < x < x_n) \\ -eN_A & (-x_p < x < 0) \end{cases}$$

(2.1)

であるとする。ここでeは電気素量、 $N_D$ ,  $N_A$  はそれぞれドナー、アクセプター濃度、 $x_p$ ,  $x_n$  は p 型、n 型半導体中の空乏層の厚さである。また検出器全体の正味の電荷はゼロであるので、

$$N_A x_p = N_D x_n \tag{2.2}$$

である。検出器中の任意の点での電位  $\varphi(x)$  はポアソン方程式

$$\frac{d^2\varphi(x)}{dx^2} = -\frac{\rho(x)}{\varepsilon} = \begin{cases} -\frac{eN_D}{\varepsilon} & (0 < x < x_n) \\ \frac{eN_A}{\varepsilon} & (-x_p < x < 0) \end{cases}$$

(2.3)

に従う。ここで  $\varepsilon$  はシリコンの誘電率である。この式を積分すると電場 E(x) が求まるわけであるが、電荷分布の両端  $(x=-x_p,x_n)$  で電場が 0 になるという境界条件を適用すると、電場 E(x) は

$$E(x) = -\frac{d\varphi(x)}{dx} = \begin{cases} \frac{eN_D}{\varepsilon}(x - x_n) & (0 < x < x_n) \\ -\frac{eN_A}{\varepsilon}(x + x_p) & (-x_p < x < 0) \end{cases}$$

(2.4)

となる。

もう一度この式を積分すると電位分布  $\varphi(x)$  が求められる。境界条件として、p-n接合電圧を  $V_0$ 、バイアス電圧を V として、

$$\varphi(x_p) = 0, \ \varphi(x_n) = V + V_0 \tag{2.5}$$

を適用すると、電位分布 φ は

$$\varphi(x) = \begin{cases} -\frac{eN_D}{2\varepsilon} (x - x_n)^2 + (V + V_0) & (0 < x < x_n) \\ \frac{eN_A}{2\varepsilon} (x + x_p)^2 & (-x_p < x < 0) \end{cases}$$

(2.6)

となる。さらにx=0での連続条件から

$$\varphi(x=0)(0 < x < x_n) = \varphi(x=0)(-x_p < x < 0)$$

(2.7)

が要求されるので、

$$V + V_0 = \frac{e}{2\varepsilon} (N_D x_n^2 + N_A x_p^2)$$

(2.8)

となる。式(2.8)と式(2.2)から

$$x_n = \sqrt{\frac{2\varepsilon(V + V_0)}{eN_D(1 + \frac{N_D}{N_A})}}, \ x_p = \sqrt{\frac{2\varepsilon(V + V_0)}{eN_A(1 + \frac{N_A}{N_D})}}$$

(2.9)

が得られ、さらに空乏層の厚み d は

$$d = x_n + x_p = \sqrt{\frac{2\varepsilon(V + V_0)}{e} (\frac{1}{N_D} + \frac{1}{N_A})}$$

(2.10)

となる。

いまドナー濃度がアクセプター濃度よりずっと高い場合  $(N_D \gg N_A)$  の p-n+接合を考える。式 (2.2) より、 $x_n \gg x_n$  となる。従って、式 (2.10) より空乏層の厚さ d は

$$d \cong x_p = \sqrt{\frac{2\varepsilon(V + V_0)}{eN_A}} \tag{2.11}$$

と近似できる。逆に  $N_A\gg N_D$  の p<sup>+</sup>-n 結合を考えると、式 (2.11) で  $N_A$  の代わりに  $N_D$  を入れた式が求まる。従って、空乏層の厚さの一般的な解は、

$$d \cong \sqrt{\frac{2\varepsilon(V+V_0)}{eN}} \tag{2.12}$$

となる。 ここで、N は不純物濃度 (ドナーあるいはアクセプターのいずれか) である。半導体の比抵抗

$$\rho = \frac{1}{e\mu N}

\tag{2.13}$$

を使って空乏層の厚さ dを書き直すと

$$d = \sqrt{2\varepsilon(V + V_0)\mu\rho} \tag{2.14}$$

となる。ここで  $\mu$  は多数キャリアの移動度である。式 (2.14) より、同じバイアス電圧で広い空乏層を得るには、大きな比抵抗を持つ物質が望ましい事が分かる。

# 2.2 シリコンストリップ検出器

シリコンストリップ検出器は高い位置分解能、応答の高速性、高い検出効率、さらに小型化し易いなどの利点から、高エネルギー実験で広く使われている。SCT もシリコンストリップ検出器であり、その構造を以下に示す。

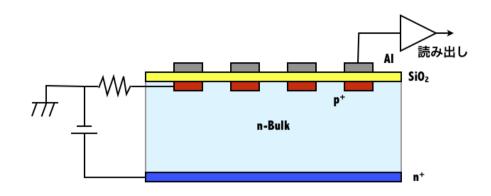

図 2.7 にシリコンストリップ検出器の構造の概念図を示す。高純度の n 型半導体 (以下、n バルク) の片面のみに  $p^+$  型半導体をストリップ状に埋め込み ( $p^+$  インプラント)、反対側には逆バイアス電圧を印加する電極として  $n^+$  半導体が全面に形成されている。p-n 接合は  $p^+$  ストリップと n バルクの界面に生じ、逆バイアス電圧を加える事により、 $n^+$  面に向かって空乏層が広がる。このようにしてできた空乏層を荷電粒子が通過すると、荷電粒子の落としたエネルギーに比例した数の電子・正孔対が生じ、正孔は  $p^+$  ストリップに、電子は  $n^+$  面に引き寄せられる。 $p^+$  ストリップの表面には絶縁体の層 (図 2.7 では  $SiO_2$ ) があり、ストリップの上にはアルミの電極がはられている。この電極とストリップは容量的に結合 (AC 結合) していて、ストリップに集まった電荷により、アルミ電極に電荷が誘起され、信号として読み出される。信号を出力したストリップの位置から荷電粒子の位置を一次元的に決定できる。こ

図 2.7: n バルク p+ ストリップ型検出器

れがシリコンストリップ検出器の動作原理である。現行の SCT はこの n バルク  $p^+$  ストリップ構造である。

一方、アップグレード用新型 SCT は次に説明する p バルク  $n^+$  ストリップ構造である。これは、次の 2.3 で述べるように放射線耐性に優れている。図 2.8 に p バルク  $n^+$  ストリップ構造をもつシリコンストリップ検出器の概念図を示す。原理は上で説明した n バルク  $p^+$  ストリップ構造のものと同じである。ただし、p バルク  $n^+$  ストリップ構造の場合、絶縁体の層(図 2.8 では  $SiO_2$ )と p バルクの界面に正電荷が蓄積する事により、その電界に引き寄せられた電子が p バルク部表面に電子層を形成する。その結果、 $n^+$  ストリップ間が電気的につながってしまう。したがって、隣り合う  $n^+$  ストリップを電気的に分離させる必要がある。分離の方法の一つとして、 $n^+$  ストリップの間に  $p^+$  ストリップを埋め込む方法がある。この  $p^+$  ストリップを p ストリップと呼ぶ。

図 2.8: pバルク n+ ストリップ型検出器

# 2.3 放射線損傷

シリコン半導体検出器は放射線損傷による性能の劣化が起こる。最も重要な損傷は放射線がシリコン結晶を通過する事による、バルク中の格子の損傷 (格子欠陥)である。

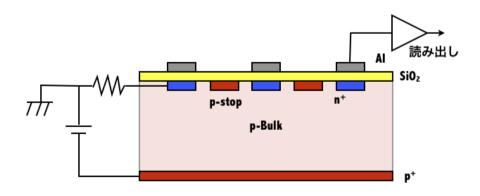

n型半導体に放射線を照射し続けると、半導体中のドナーの濃度は照射とともに減少し、さらにはアクセプターの様に振る舞う格子欠陥が増え、 $\sim 10^{12} \ / \mathrm{cm}^2$  の照射量で p型への転換が観測されるようになる。これは型変換として知られている [5]。

全空乏化電圧 $V_{fd}$ は式(2.12)から

$$V_{fd} = \frac{ed^2}{2\varepsilon} |N_{eff}| - V_0 \tag{2.15}$$

と書ける。ここで、 $N_{eff}$  はシリコン中の実効不純物濃度である。このように、全空乏化電圧は実効不純物濃度に比例するので、実効不純物濃度の変化に伴って全空乏化電圧も変化する。図 2.9 に n 型バルクセンサーに放射線照射した時の放射線照射量  $\Phi_{eq}$  に対するバルク部の実効不純物濃度と全空乏化電圧の変化の様子を示す [6]。 $\sim 2 \times 10^{12} \ / \mathrm{cm}^2$  の放射線量で型変換し、その後放射線照射量に比例して実効不純物濃

図 2.9: 放射線量に対しての不純物濃度と全空乏化電圧の変化

度と全空乏化電圧は増加していく。

n バルク  $p^+$  ストリップ構造である現行の SCT の場合、型変換前では p-n 接合は  $p^+$  ストリップと n バルクの界面に生じ、逆バイアス電圧を加えると  $n^+$  面に向かって空 乏層が広がる。しかし、型変換後バルクが p 型になった場合、p-n 接合は  $n^+$  面とバ

ルクの界面に生じ、逆バイアス電圧の印加により、空乏層は p<sup>+</sup> ストリップに向かって広がる。図 2.10 は型変換前後での現行 SCT の空乏化の様子である。したがって、

図 2.10: 放射線損傷による型変換前後での現行 SCT の空乏化の様子

放射線損傷による型変換後のシリコンセンサーにおいて、入射粒子により生成される正孔を再結合で失わずに p<sup>+</sup> ストリップで読み出すためには、センサーを全空乏化する必要がある。

現行の SCT は、LHC の 10 年間の運転の間に  $\sim 2\times 10^{14}/\mathrm{cm}^2$  の 1 MeV の中性子が通過するのと同等の放射線損傷を受ける。図 2.9 よりこの放射線量を受けた時の全空乏化電圧は  $\sim 600$  V である事が分かる。SCT の最高運転電圧は 500 V であるため、10 年間の運転の間に SCT は全空乏化状態での動作が不可能となる。そうなると、入射粒子により生成された正孔は  $p^+$  ストリップに到達する前に再結合し、読み出される電荷量が減少する。その結果、ノイズに比べ信号量が十分でなくなり、tracking efficiency の減少、fake track の増大を引き起こし、飛跡検出器としての性能が満たされなくなる。

一方、pバルク  $n^+$ ストリップ構造を持つセンサーの場合、放射線損傷を受けても型変換をおこさないため、常に  $n^+$  ストリップから空乏層が広がる。そのため、もし全空乏化電圧が運転最高電圧を越えた場合でも、部分空乏化状態で検出器として使用できる。この場合、入射粒子により生成される電子正孔対は全空乏化状態に比べると少ないものの、生成された電子を再結合で失うことなく  $n^+$  ストリップで読み出す事ができる。このような理由により現在開発中のアップグレード用新型 SCT は  $n^+$  ストリップ構造を持つ予定である。

以上のように放射線損傷に関してはpバルク $n^+$ ストリップ構造が優位であるが、電極間分離の処置をする分、nバルク $p^+$ ストリップより構造が複雑であり製造が困

難である。またpストップがあるとそのエッジ部分で強電場が発生してしまう。その結果、放電が発生し、それがノイズの原因になるなどのデメリットもあるので、LHCではnバルクセンサーを使用している。しかし、放射線損傷がさらに増える SLHCではpバルクセンサーを使用せざるを得ない。

# 第3章 ABCNチップ

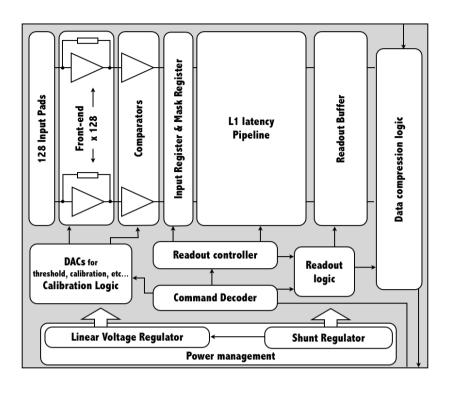

ABCN チップは ATLAS アップグレード用の新型 SCT に搭載される読み出しチップであり、1つの ABCN チップで 128本のストリップの読み出しができる。128本のストリップからの入力信号は信号増幅後、設定された閾値に基づきヒットのあり・なしが判断され、ヒットがあったかどうかという情報がバッファに保持される。その後、ある一定時間内に、蓄積されたヒット情報を外部に送り出すタイミングを決定する信号 (L1トリガー) を受けると、どのストリップにヒットがあったのかというデータが外部へ送信される。

本研究で新型 SCT テスト用読み出しシステムを開発するにあたり、読み出しの対象である ABCN チップを理解する事は重要である。この章では ABCN チップについての詳細を説明する。

# 3.1 各ブロックの説明

図 3.1 に ABCN チップのブロック図を示す。主なブロックは

- Front-end

- Comparators

- Input Register & Mask Register

- Pipeline

- Readout Buffer

- Data Compression Logic

- Readout Logic

- Readout Controller

- Command Decoder

- Calibration Logic

図 3.1: ABCN チップのブロック図

である。各ブロックの詳細を説明する前に、以下でデータの流れを大まかに説明する。 128 本のストリップからのアナログ信号はまず Front-end で増幅、波形整形される。その後、Comparators の閾値以上の信号がヒットと判断され、デジタル信号で Pipeline に送られる。ABCN チップが L1 トリガーを受けると、Pipeline から L1 トリガーで指定されたタイミングとその前後の合計 3 イベント分のヒット情報が Readout Buffer へ送られる。Readout Buffer にデータが入ると、Data Compression Logic が Readout Buffer からデータを順次読み出し、最終的なデータ量を減らすためにデータフォーマットを変更・圧縮する。その処理を受けたデータは Readout Logic を経由して、Readout Controller でデータ出力ピンから外部へ出力される。

以下でそれぞれのブロックについての詳細を説明する。

#### 3.1.1 Front-end

#### Preamplifier-Shaper

Preamplifier で信号を増幅し、Shaper で波形の整形をする。ゲインの設計値は  $100 \,\mathrm{mV/fC}$  である。線形性は  $\pm 6 \,\mathrm{fC}$  までの入力に対して  $3 \,\%$ 以下、 $\pm 10 \,\mathrm{fC}$  までの入力では  $10 \,\%$ 以下である。パルスの立ち上がりは  $22 \,\mathrm{ns}$  である。ノイズはストリップ長  $2.5 \,\mathrm{cm}$  のシリコンセンサーをつけた時、 $750 \,\mathrm{e}$  以下になるように設計されている。

#### 3.1.2 Comparators

ノイズと信号を区別するために、設定された閾値電圧と増幅された信号の電位を 比較し、閾値よりも信号の方が大きければヒットがあったと判断する。

閾値電圧は ABCN チップ内部にある Threshold DAC により設定できる。この DAC の値はチップ内部のレジスタの一つである Threshold Register に書き込んでおく。閾値は  $\pm 9$  fC の範囲で指定できる。また各チャンネル毎の閾値のオフセットのばらつきは Trim DAC により調整でき、この DAC の値もチップ内部のレジスタの一つである Trim DAC Register に書き込んでおく。

## 3.1.3 Input Register & Mask Register

#### Input Register

Front-end からきたデータを保持し、動作クロック (40 MHz) に同期した信号をつくる。

#### **Edge Detection Circuitry**

Edge Detection Circuitry は Input Register 内部の回路であり、以下の2つのモードのいずれかで動作する。

エッジ検出 'ON':

Comparator がヒットのない状態からヒットのある状態に変化したと判断した 1クロック周期の間だけ同期した信号を生成する。

エッジ検出 'OFF':

Comparator がヒットと判断している間だけ同期した信号を生成し続ける。

どちらのモードで動作するかは、チップ内部のレジスタの一つである Configuration Register1 中の 1 bit により指定する。

#### Mask Register

Mask Register は以下の2つのモードのいずれかで動作する。

• Channel Masking Mode:

Front-endへの入力信号の大きさによらず、各チャンネルのヒットを強制的にないこと (=mask) にする機能。例えば、ノイズの大きいストリップからの信号を無視する事を可能にする。mask するチャンネルは Mask Register の bit pattern で指定する。

#### • Test Pulse Mode :

Front-end への入力とは無関係に Mask Register の値に従い、hit pattern を生成する。

Mask Register の値を mask パターンにするかテストパターンにするかは、Configuration Register1 中の1 bit で指定する。

#### 3.1.4 Pipeline

Pipeline は Input Register からのヒット情報を保持する。動作クロックが 40 MHz なので 25 ns 毎に各チャンネルにヒットがあったかどうかが記憶されている。L1トリガーを受けると、対応するイベントとその1クロック前と1クロック後ろの合わせて3イベント分のデータが読み出される。

Pipeline は 2 つの dual port RAM block で構成される。Pipeline の幅は 144bit で、そのうち 128 bit が 128 チャンネル分のヒットデータに対応しており、8 bit がバンチ衝突の回数 (イベント数のようなもの) に対応している。1 つの RAM block の深さは 128 bit なので、Pipeline の合計の深さは 256 bit (=128 bit×2) である。Pipeline は 40 MHz のクロックで動作しているので、Pipeline に 6.7  $\mu$ s (=25 ns×256) 間のデータを保持することができる。

#### 3.1.5 Readout Buffer

L1トリガーを受け、Pipelineから出力されたヒット情報は、読み出されるまでReadout Buffer に保存される。

Readout Buffer の幅は 180 bit で、そのうち 128 bit が 128 チャンネル分のヒットデータに、4 bit が L1 トリガーの回数に、8 bit がバンチ衝突の回数にそれぞれ対応している。深さは 128 bit である。L1 トリガー毎に 3 イベント分のデータ(3 bit)を保持するので、この深さで L1 トリガー 42 回分からのデータ(3 bit×42=126 bit)を保存できる。

# 3.1.6 Data Compression Logic

Data Compression Logic は、最終的なデータ量を減らすために Readout Buffer 中のデータフォーマットを変更・圧縮する。

Data Compression Logic は、Readout Buffer にデータが存在すれば、イベント毎に組み立てられた 3 個 (L1トリガーで指定されたタイミングとその前後) の 128-bit words を読み出す。その後、データの順序を 128 個の 3-bit words へ並べ替え、各チャンネルの 3 bit のヒットパターンに対して、表 3.1 で示す評価基準と比較する。もし

ヒットパターンが評価基準に合致すれば、"datavalid"と呼ばれる信号を発行する。合致しなければ、そのチャンネルからのデータはなく、次のチャンネルからのヒットパターンを検査する。この過程は、128 チャンネルすべてに対して繰り返され、すべてのチャンネルの検査が終わると"end"と呼ばれる信号を発行する。

表 3.1: データ圧縮の評価基準 (ここで X は'0' か'1' のどちらか)

| どのモードかの選択は、Configuration Register1 中の 2 bit で決まる。 |

|---------------------------------------------------|

|---------------------------------------------------|

| モード (1:0) | 評価基準  | ヒットパターン           | 使用例                |

|-----------|-------|-------------------|--------------------|

| 00        | Hit   | 1XX or X1X or XX1 | Detector alignment |

| 01        | Level | X1X               | Normal Data Taking |

| 10        | Edge  | 01X               | Normal Data Taking |

| 11        | Test  | XXX               | Test Mode          |

#### 3.1.7 Readout Logic

Readout Logic は、daisy-chainで互いに接続されたチップ間で、"token"と呼ばれる信号の受け渡し行い、チップからの信号読み出しのタイミングを制御する。

"token"信号が来ると、チップは"datavalid"信号が発行されているか確認し、されていれば"end"信号までのデータを読み出し、Readout Controllerへ送る。データをすべて読み出し終わると、次のチップに"token"信号を渡す。

#### 3.1.8 Readout Controller

Readout Controller は、daisy-chainで接続されている複数の ABCN チップ間のデータの流れを制御する。

それぞれの ABCN チップは"Master"、"End"、"Slave"のいずれかに設定する。"Master"チップは L1トリガーを受け取ると、"token"信号を daisy-chain で接続されているチップに送信する。"token 信号を受けた"Slave"チップは"Master"チップの Readout Controller に順次データを送る。"End"チップからのデータを受け取った"Master"チップはデータ出力ピンから外部にデータを出力する。

チップを"Master", "Slave", "End"のどれに設定するかは、Configuration Register1中の2 bit で指定する。

#### 3.1.9 Command Decoder

Command Decoder は、ABCN チップのコマンド入力ピンに入力された bit stream (コマンド)をデコードする。そのデコードされた内容に応じて、ABCN チップ内部 の各レジスタや各ブロックを制御する。実際にどういったコマンドがあり、それぞれのコマンドがどのような bit stream であるかなどの詳細は 3.3 Control Protcol で説明する。

### 3.1.10 Calibration Logic

ABCN チップは、センサーからの入力だけではなく、チップをテストするために自分自身で電荷を Front-end に入力できる。Calibration Logic は Front-end にある Calibration 回路へ入力パルス送る。Front-end 内の Calibration 回路に送られた入力パルスは、表 3.2 に示すようなチャンネルの分類に基づき、32 チャンネル 1 組のグループのいずれかに送られる。4 つあるグループのどのグループにパルスを入力するかは、Configuration Register1 中の 2 bit により指定する。

| モード (1:0) | パルス入力されるチャンネル         |

|-----------|-----------------------|

| 00        | in3, in7, in11,,in127 |

| 01        | in2, in6, in10,,in126 |

| 10        | in1, in5, in9,,in125  |

| 11        | in0, in4, in8,,in124  |

表 3.2: Calibration モード

Front-end に入力する電荷量は、チップ内部のレジスタの一つである Calibration Register の値で指定でき、 $0.04~\rm{fC}$  ステップで  $0\sim10.2~\rm{fC}$  の範囲で設定できる。チップの動作クロックの立ち上がりと入力パルスの入射タイミングの相対的な遅延も Calibration Register の値によって指定する。

# 3.2 Registers

ABCN チップを制御するための設定を保持するレジスタである。表 3.3 に ABCN チップ内部の主なレジスタをまとめる。チップを動かす前にこれらのレジスタに適当な値を設定する必要がある。

表 3.3: ABCN チップ内部の主なレジスタのリスト

| レジスタの名前                        | 長さ  | 機能                 |  |

|--------------------------------|-----|--------------------|--|

| Configuration Register1 (CFG1) | 16  | Configuration      |  |

| Configuration Register2 (CFG2) | 16  | IO drive           |  |

| Threshold Register (ThreshReg) | 16  | Main Threshold     |  |

| Bias Register1 (BiasReg1)      | 16  | FECurrent Bias     |  |

| Bias Register2 (BiasReg2)      | 16  | FECurrent Bias     |  |

| Bias Register3 (BiasReg3)      | 16  | FECurrent Bias     |  |

| L1 Delay Register (L1DelayReg) | 16  | L1 Latency setting |  |

| Test/Mask Register (Test/Mask) | 128 | Test/Mask Register |  |

| Calibration Register (CalReg)  | 16  | Cal pulse delay    |  |

| Trim DAC Register (TrimReg)    | 16  | Trim DAC register  |  |

## 3.3 Control Protocol

チップを制御するコマンドは"L1 Trigger Command" と"Control Commands"の2つに大別できる。さらに"Control Commands"には"Fast Control Commands"と"Slow Control Commands"の2つのタイプがある。

"L1 Trigger Command" および" Fast Control Commands" はデータ収集時に使い、"Slow Control Commands" は各種のレジスタの値を書き換え、チップの初期化、Front-end の Calibration 回路にパルスを入力する際に使う。それぞれのコマンドに対するパケットを表 3.4 に、さらに"Slow Control Commands" のパケットの一覧を表 3.5 に示す。

表 3.4: コマンドのフォーマット

| Type    | Field 1 | Field 2 | Field 3 | Description                         |

|---------|---------|---------|---------|-------------------------------------|

| Level 1 | 110     |         |         | L1 Trigger                          |

| Fast    | 101     | 0100    |         | Soft Reset                          |

|         |         | 0010    |         | BC Reset                            |

| Slow    | 101     | 0111    | Command | Slow Control Command, see Table 3.5 |

ABCN チップに制御コマンドを送った時に、コマンドがどのような流れで処理されるかを以下に記す。

1. ABCN チップにコマンドを送ると、Command Decoder に入る。そこでまずコマンドの最初の 3 bit (Field 1) がデコードされる。その結果、入力コマンド

表 3.5: Slow Control 用のコマンド

| Field 3                               | Field 4 | Field 5 | Field 6             | Description                         |

|---------------------------------------|---------|---------|---------------------|-------------------------------------|

| 0001,1101                             | aaaaaaa | 000 000 | dddd,dddd,dddd,dddd | Write Configuration Register 1      |

| , , , , , , , , , , , , , , , , , , , |         |         | aaaa,aaaa,aaaa,aaaa | 0 0                                 |

| 0000,1101                             | aaaaaaa | 000 001 | 1/100111            | Read Configuration Register 1       |

| 1001,1101                             | aaaaaaa | 001 000 | dd(128 bit)         | Write Mask Register                 |

| 0001,1101                             | aaaaaaa | 001 100 | dddd,dddd,dddd,dddd | Write Configuration Register 2      |

| 0000,1101                             | aaaaaaa | 001 101 |                     | Read Configuration Register 2       |

| 0001,1101                             | aaaaaaa | 010 000 | dddd,dddd,dddd,dddd | Write Calibration Register          |

| 0000,1101                             | aaaaaaa | 010 001 |                     | Read Calibration Register           |

| 0001,1101                             | aaaaaaa | 011 000 | dddd,dddd,dddd,dddd | Write Threshold Register            |

| 0000,1101                             | aaaaaaa | 011 001 |                     | Read Threshold Register             |

| 0000,1101                             | aaaaaaa | 100 000 |                     | Instr. Test Pulse to Input Register |

| 0000,1101                             | aaaaaaa | 101 000 |                     | Instr. Enable Data Taking Mode      |

| 0000,1101                             | aaaaaaa | 110 000 |                     | Instr. Issue Calibration Pulse      |

| 0001,1101                             | aaaaaaa | 111 000 | dddd,dddd,dddd,dddd | Write Bias Register 1               |

| 0000,1101                             | aaaaaaa | 111 001 |                     | Read Bias Register 1                |

| 0001,1101                             | aaaaaaa | 111 010 | dddd,dddd,dddd,dddd | Write Bias Register 2               |

| 0000,1101                             | aaaaaaa | 111 011 |                     | Read Bias Register 2                |

| 0001,1101                             | aaaaaaa | 111 100 | dddd,dddd,dddd,dddd | Write Bias Register 3               |

| 0000,1101                             | aaaaaaa | 111 101 |                     | Read Bias Register 3                |

| 0001,1101                             | aaaaaaa | 000 100 | dddd,dddd,dddd      | Write Trim DAC                      |

| 0000,1101                             | aaaaaaa | 000 101 |                     | Read Trim DAC                       |

| 0000,1101                             | aaaaaaa | 011 101 |                     | Read Fuse Register                  |

| 0001,1101                             | aaaaaaa | 010 100 | dddd,dddd,dddd      | Write L1 Delay Register             |

| 0000,1101                             | aaaaaaa | 010 101 |                     | Read L1 Delay Register              |

| 0000,1101                             | aaaaaaa | 101 101 |                     | Read Status Register 1              |

| 0000,1101                             | aaaaaaa | 110 101 |                     | Read Status Register 2              |

|                                       |         |         |                     |                                     |

Field 3: この後に続く bit stream の長さ (8 bit)

Field 4: チップアドレス (7 bit) Field 5: コマンドの種類 (6 bit)

Field 6: レジスタに書き込む値 (Mask Register 以外: 16 bit, MaskRegister: 128 bit)

は"L1 Trigger Command"と"Control Commands"の2つの大別される。

- 2. 1. で"L1 Trigger Command"と認識されると、Pipeline からデータが読み出される。1. で"Control Command"と認識されたコマンドは、3 bit に続く次の4-bit (Field 2) がデコードされ、"Fast Control Commands"と"Slow Control Commands" の2つのタイプにさらに分類される。

- 3. 2. で"Fast Control Command"と認識されると、対応するコマンドが実行される。2. で"Slow Control Command"と認識されたコマンドは、次に続く bit (Field 3) が順次デコードされていき、"Slow Control Command"の中でもさらに分類される。デコードが終わると、対応するコマンドが実行される。

以下でさらに"L1 Trigger Command", "Fast Control Command", "Slow Control Command"についてそれぞれ説明する。

#### L1 Trigger Command

"L1 Trigger Command"は高頻度で送る必要があるため、すべてのコマンドの中で最も短いパケットである。daisy-chain で接続されたすべての ABCN チップがこのコマンドに反応する。チップがこのコマンドを受けると、L1 delay time で前もって指定されたイベントとその前後合わせて 3 イベント分のデータが Readout Buffer に送信される。その後データは 3.1 で説明した処理を経て自動的に外部に出力される。

#### Fast Control Command

"Fast Control Commands"には"Soft Reset"コマンドと"BC Reset"コマンドがある。"Soft Reset"コマンドはPipelineの値をすべて0にするために送り、"BC Reset"コマンドはバンチ衝突回数をカウントしているBunch Crossing (BC) counterの値を0にするために送る。Daisy-chainで接続されたすべてのABCNチップがこれらのコマンドに反応する。これらのコマンドでチップ内部のレジスタの値は変化しない。

#### **Slow Control Commands**

"Slow Control Command"はレジスタの値を変更し、任意の状態にチップを初期化したり、Front-end の Calibration 回路にパルスを入力するためのコマンドである。表 3.5 に示したように、チップアドレスやレジスタに書き込む bit stream からなる長いパケットである。チップアドレスに Global Address である'1111111' を指定した場合、すべてのチップがこれらのコマンドに反応する。それ以外の場合、指定されたアドレスのチップのみがこれらのコマンドに反応する。

# 3.4 チップの状態

ABCN チップには以下の3つの状態が存在する。

- Send\_ID Mode チップのレジスタの値を変更する状態

- Read Register Mode

設定されたレジスタの値を確認する状態

- Data Taking Mode ヒットデータを出力する状態

状態の初期化の方法や、L1トリガーを送った時の出力がそれぞれの状態で異なる。 以下でそれを説明する。

#### Send\_ID Mode

電源を入れた直後や"Write Register"コマンドを送ると、チップはこの状態になる。この状態で、L1トリガーをチップに送ると、チップは自身のチップアドレスと設定された Configuration Register1 の値を出力する。

#### Read Register Mode

"Read Register"コマンドを送ると、チップはこの状態になる。この状態で、L1トリガーをチップに送ると、チップはチップアドレスとレジスタの値を出力する。

#### **Data Taking Mode**

"Enabe Data Taking"コマンドを送ると、チップはこの状態になる。この状態で、L1トリガーをチップに送ると、チップはヒットデータを出力する。

#### Clock Feed Through

"Master"として初期化されたチップの Configuration Register1 に割り振られている clock feed through の bit が OFF の時、チップは入力されたクロックをそのまま出力する。この機能は簡単なシステムテストの時に役立つ。

# 第4章 試験用読み出しシステム

本研究では新型 SCT 用のプロトタイプ検出器を試験するための読み出しシステムを開発した。読み出しシステムは、SEABAS と呼ばれる汎用読み出し基板と、PC (Linux, Mac) 上で動作する C/C++で記述されたソフトウェアから構成される。この章では、まず汎用読み出し基板 SEABAS について紹介し、その後、開発したデータ収集 (DAQ) システムの説明を行う。最後に DAQ システムの動作試験について述べる。

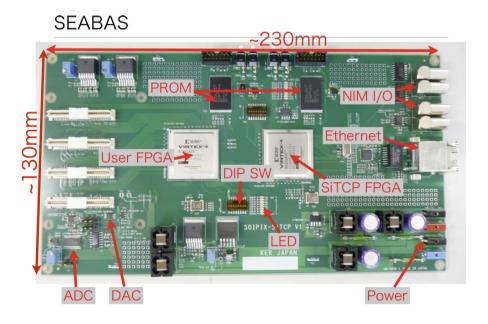

# 4.1 汎用,読み出し基板 SEABAS

SEABAS は Silicon-On-Insulator (SOI) 技術を応用したピクセル型半導体検出器を開発したグループによって開発された読み出し基板である [8]。図 4.1 に SEABAS の写真を示す。大きさは 240 mm×130 mm である。

図 4.1: SEABAS

SEABAS は、User FPGA と SiTCP FPGA と呼ばれる 2 つの FPGA を搭載している。User FPAGA は、試験するデバイスを制御するためにユーザーが自由に使うこ

とができる。SiTCP FPGA は、外部とのデータ通信を行うためのものでユーザーが 手を加える必要は無い。

SiTCP は FPGA 上で TCP/IP の処理を実現したネットワークプロセッサである。 TCP の処理を FPGA で行うことにより、SiTCP は 95 Mbps 程度の安定した通信速度を実現している。SiTCP は Ethernet 経由で外部 PC とのデータ送受信を行う。また SiTCP は TCP だけではなく UDP を用いて PC から User FPGA 内部のレジスタを操作するインターフェイスを持つ。これは Remote Bus Control Protocol (RBCP)と呼ばれる。これにより、User FPGA 内部の最大 256 個のレジスタを PC から操作できる。

SEABAS を用いた DAQ システムでは、PC との通信を SiTCP FPGA が自動的 に処理するため、ユーザーは読み出したいデバイスに応じて User FPGA のファーム ウェアを変更するだけで、DAQ システムを構築できる。SiTCP は FIFO と同じよう なインターフェイスになっているので、User FPGA 内で FIFO にデータを読み書き するのとほぼ同じ操作で、SiTCP 経由のデータ通信を確立することができる。

SEABAS・PC 間は TCP/IP による Ethernet で接続されるため、さらに CAMAC や VME クレート等を使用する必要がない。SEABAS が 130 mm×230 mm と小さいことと合わせ、DAQ システム全体を小型化できる。また SEABAS を用いた DAQ システムでは、Ethernet のインターフェイスを持つ一般的な PC と SEABAS さえあればデータ収集ができるため、特別な準備なしに様々な場所で実験を行える。

以上の事実のように、SEABAS を用いた DAQ システムの特徴は高い汎用性と利便性である。

#### 4.1.1 SEABAS **の仕様**

以下に SEABAS のスペックを示す。

• SiTCP FPGA

Xilinx Vertex4 (XC4VLX15-10FF668)

最大ブロック RAM: 864 kbit

100BASE-T 規格の SiTCP (帯域上限 100Mbps)

• User FPGA

Xilinx Vertex4 (XC4VLX25-10FF668)

最大ブロック RAM : 1,296 kbit

120 本の I/O 線が sub card 接続用のコネクタと繋がっている。DAC、NIM I/O の制御もこの FPGA が行う。

#### • DAC

National Semiconductor 製 DAC124S085 4 系統の 12bit の D/A Converter 。最大出力電圧は 3.3 V。

#### • Power

$\pm 5$ V を入力する。プラス側は約 1A、マイナス側は約 0.2A 流すことの出来る外部電源を使用。

#### • NIM I/O

Input/Output それぞれ2系統ずつ (LEMO コネクタ)。

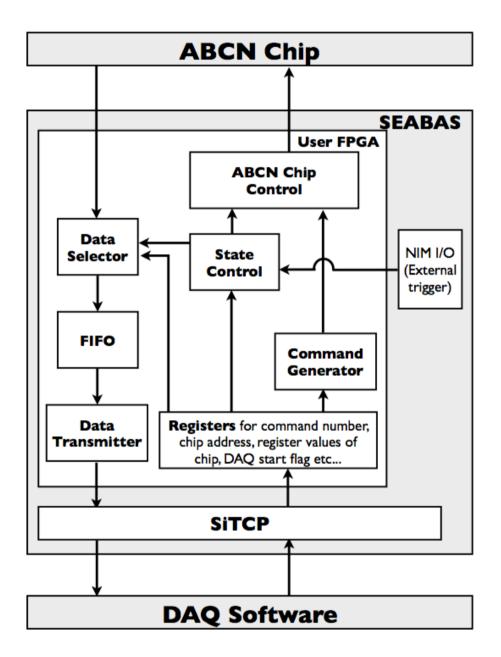

### 4.1.2 読み出し用ファームウェア

読み出し用ファームウェアは、User FPGA と SiTCP FPGA に実装されたプログラムからなっている。SiTCP FPGA は SiTCP 専用で、すでにプログラムが実装されている。本研究では User FPGA に 2 つの機能を実装するためのファームウェア開発を行った。

User FPGA の機能の1つは、ABCN チップを制御する事である。前章で説明した通り、チップを制御するためのbit stream (コマンド) を送る事によってチップの状態や内部レジスタの値を変更するための仕組みを作る。具体的には、User FPGA 内のレジスタを PC から操作し、そのレジスタの値に一対一対応したコマンドを SEABAS がチップに送るようにした。

もう1つの機能は、ABCN チップから送られてくるデータを受信し、それを PC へ送信する事である。前に述べたように、User FPGA からは SiTCP が単なる FIFO の様に見えるため、FIFO にデータを読み書きするのとほぼ同じ動作を行えば SiTCP 経由で、データの送受信を PC と行える。

図 4.2 に DAQ システムのブロック図を示す。そこに示されているように、User FPGA に実装するファームウェアは複数の機能ブロックで構成される。以下でそれぞれのブロックについて説明する。

#### • Registers

SiTCP の機能の一つである RBCP (UDP) を用いて、PC から変更可能なレジスタ。最大 256 個のレジスタを PC から操作できる。このレジスタに以下の値を割り当てておく。

- DAQ 開始信号

- チップに送るコマンドを指定する番号 (コマンド番号)

- チップアドレス

図 4.2: DAQ システムのブロック図

### - ABCN チップ内部の各種レジスタに書き込む値

### • Command Generator

Registers に保持されているチップアドレスや ABCN チップ内部の各種レジスタに書き込む値に基づいて、表 3.4、表 3.5 にある ABCN チップに送るすべてのコマンドをあらかじめ組み立て、番号付けして、保持しておく。PC からコマンド番号を指定されると (正確には変更された時のみ)、保持してあったコマンドからその番号に対応したコマンドを ABCN Chip Control に送る。

### • State Control

コマンド番号に応じて4つのシステムの状態を作り、それらの状態を制御する。 それぞれの状態は、PCからコマンド番号の変更を待っている状態、チップに リセットを送る状態、チップにL1トリガーコマンドを送る状態、チップにコ ントロールコマンド(L1トリガーコマンド以外のコマンド)を送る状態である。

### • ABCN Chip Control

ABCN チップの制御を行う。具体的には、State Control で決められたシステムの状態に応じて、リセットや L1 トリガーコマンド、コントロールコマンドを ABCN チップに送る。

### • Data Selector

ABCN チップにL1トリガーコマンドを送ると、ABCN チップはデータを出力する。Data Selector ではチップから出力されたデータの始まりと終わりを判断し、FIFO に入れるデータを選択する。

### • FIFO

Write のクロックと Read のクロックが異なる非同期 FIFO である。Data Selector で選ばれたデータを保持する。

### • Data Transmmiter

FIFO にデータがある場合、SiTCP を介して PC ヘデータを送信する。

# 4.2 読み出し用ソフトウェア

PC に実装されたソフトウェアの主な機能は、SEABASへの TCP/IP 接続の確立、TCP/IP 経由での User FPGA 内のレジスタの操作、そして SEABAS から送られて くるデータの受信である。TCP/IP データ通信のためのソケットプログラミングは C/C++を用いて記述した。

### 4.3 DAQ **の流れ**

図4.3 はDAQのフローチャートである。以下でDAQの流れについて説明する。

- 1. PC と SEABAS 間の TCP 接続を確立する。

- 2. RBCPを用いて、ABCNチップ内部の各種レジスタの初期値をPCからSEABAS に送る。SEABAS は、それらの値から ABCN チップに送るためのすべてのコマンドを組み立て、番号付けし、保持する。

- 3. ABCN チップの初期化に必要なコマンドをチップに送るため、コマンド番号を PC から指定する。その番号に対応したコマンドが ABCN チップへ順次送られる。

- 4. PC から DAQ 開始信号を SEABAS に送ると、SEABAS はデータ収集を行なう DAQ 状態になる。

- 5. PCからL1トリガーコマンドに対応するコマンド番号を指定し、ABCNチップにL1トリガーコマンドを送る。(外部トリガーでトリガーをかける場合、SEABASに搭載されている NIM I/O からの信号がトリガー信号となる。)

- 6. L1トリガーコマンドを受け取った ABCN チップは ABCN チップ内部の状態に 応じたデータを出力する。

- 7. データは FIFO に保持され、順次 PC へ送信される。そのデータを PC が受信 し、保存する。

- 8.5~7を繰り返す。

- 9. PC と SEABAS 間の TCP 接続を切る。

### 4.4 読み出したデータの解析

読み出したデータはROOTライブラリを用いたソフトウェアで解析される。ROOTとは、C++の中でヒストグラムの作成や、スクリプトの実行などを提供する CERNで開発された解析ソフトである。

図 4.3: DAQ のフローチャート (赤は送ったビットパターン、青は受け取ったビットパターン)

### 4.5 システムの動作確認

開発した DAQ システム (以下、SESABAS DAQ) を以下の2つの方法で試験した。まず、SEABAS DAQ を用いて、1 個の ABCN チップの初期化を正しく行えるかを確認した。また3章で説明したように、ABCN チップは自分自身で Front-end へ電荷を入力する事ができる。その入力パルス (以下、Calibration パルス) が任意のチャンネルに正しく入力できるかを確認した。

次に、SEABAS DAQ を用いて、20個の ABCN チップが搭載されたフレックスハイブリッド基板の性能評価テストを行った。そこで得られた結果と既存の読み出しシステム (以下、SCT DAQ) を用いて得られた結果を比較し、SEABAS DAQが正しく動作しているかを確認した。

### 4.5.1 1個の ABCN チップの読み出し

### チップの初期化

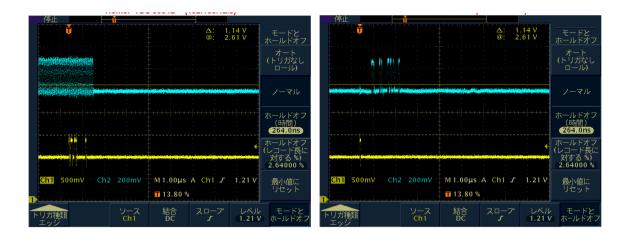

第3章で説明したように、電源をいれた直後ではチップ内部のレジスタの値はすべてクリアされているため、チップの状態は"Send\_ID Mode"で、入力されたクロックをそのまま出力する"Clock Feed Through"の状態にある。"Write Configuration Register1"コマンドをチップに送り、Configuration Register1 に適当な値を書き込めば"Clock Feed Through"から抜ける事ができる。その様子を図 4.4 に示す。"Write Configuration Register1"コマンドをチップに送った直後に、チップからのクロック送信が終わり、チップが"Clock Feed Through"から抜けたことが分かる。

"Send\_ID Mode"の状態で、L1トリガーコマンドを送ると、チップは自身のチップアドレスと設定された Configuration Register1の値を出力する。その様子を図 4.5 に示す。チップからの出力は"Send\_ID Mode"の出力として期待するビットパターンと同じであり、チップが正しく"Send\_ID Mode"の状態に初期化できている事を確認できた。"Read Register Mode"、"Data Taking Mode"でも L1トリガーコマンドを送り、チップからの出力を確認したが、期待通りのビットパターンであった。

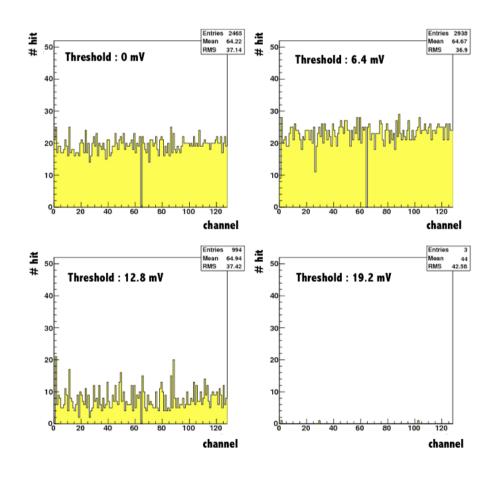

次に、SEABAS DAQ で閾値を変更できるかを確認した。ABCN チップのコンパレータの閾値は、"Write Threshold Register"コマンドをチップに送り、Threshold Register の値を書き換える事によって  $\pm 816$  mV の範囲で変更できる。ランダムトリガーを 50 回送り、各チャンネルのノイズが閾値を越える回数を測定した。これを閾値を変化させて繰り返した結果を図 4.6 に示す。閾値を上げるとノイズが閾値を越える回数が減っていることが分かる。ここで、閾値が 0 mV の時、ノイズが閾値を越える回数が 50 ではなく  $\sim 25$  である理由は、1/2 の確率で正または負になるノイズの負側のみを読み出しているからである。

図 4.4: "Clock Feed Through"から抜ける 図 4.5: "Send\_ID Mode"での L1 トリガー様子 (黄色がコマンド。青がチップからの コマンドに対するチップからの出力 (黄色出力。) がコマンド。青がチップからの出力)

図 4.6: 各閾値に対してのノイズが閾値を越える回数の変化

### Calibration パルスの入力テスト

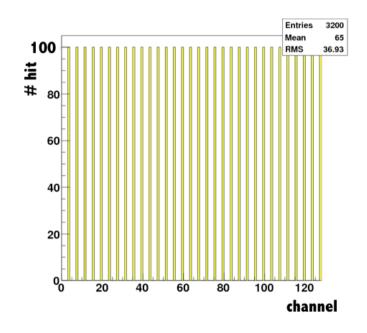

ABCN チップに"Issue Calibration Pulse"コマンドを送ると、ABCN チップは自分自身で Front-end へ Calibration パルスを入力する。Calibration パルスは表 3.2 に示した 4 つのグループのいずれかに送られる。どのグループに Calibration パルスを入力するかは"Write Configuration Register1"コマンドで Configuration Register1 の値を書き換える事で変更できる。ここではチャンネル 3, 7, 11, 15... に Calibration パルスを入力するようにグループを指定し、Calibration パルスを入力した後にトリガー送信というループを 100 回繰り返した。測定結果を図 4.7 に示す。測定結果から指定したグループのチャンネルそれぞれに 100 hit ずつあり、Calibratrion パルス入力をコントロールできていることがわかる。

図 4.7: Calibration パルス入力テスト

### 4.5.2 ハイブリッド基板の性能評価試験結果の比較

ここでは、SEABAS DAQ を用いて ABCN チップ 20 個が搭載されたフレックスハイブリッド基板の性能評価試験を行った。そこで得られた結果と SCT DAQ を用いて得られた結果とを比較し、SESABAS DAQ が正しく動作しているかを確認した。ただし、SCT DAQ では測定結果を図でしか残せない仕様になっており、ここでは測定結果の図だけを比較する。

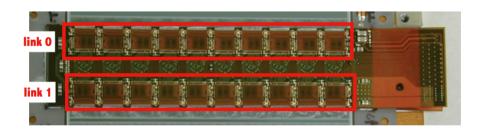

図 4.8 がテストしたフレックスハイブリッド基板である。チップ 10 個ずつが 1 つの データバスラインで接続されており、赤枠で囲まれたラインをそれぞれ link 0、link 1 と呼ぶ。

図 4.8: フレックスハイブリッド基板

### Calibration パルスのタイミング調整

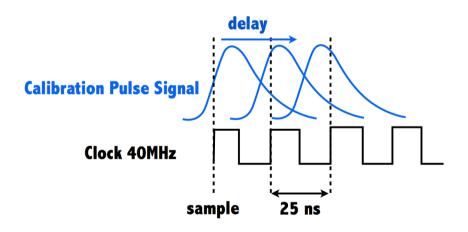

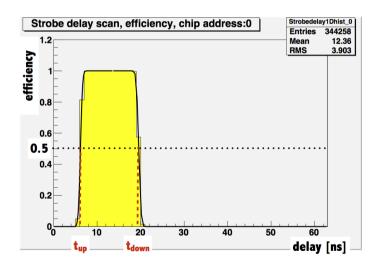

図 4.9 に示すように、Calibration パルスの入射時刻とチップの動作クロックの立ち上がりの相対的な時間差が検出効率に与える影響を調べ、Calibration パルス入力のタイミングを調整する事を strobe delay 試験と呼ぶ。ここでは、SEABS DAQ とSCT DAQ のそれぞれの strobe delay 試験の結果を比較する

図 4.9: strobe delay 試験

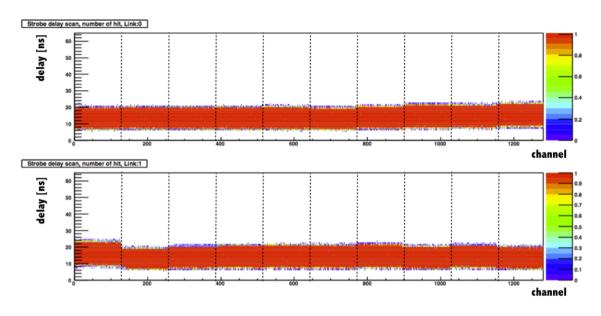

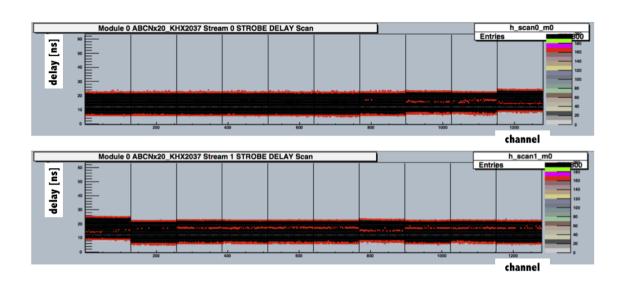

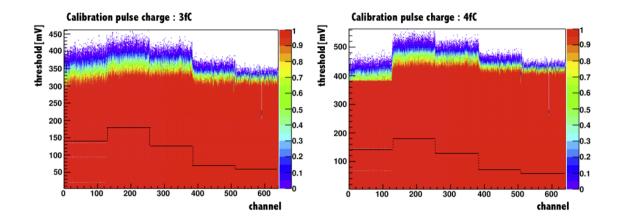

チップの動作クロックの立ち上がりと Calibration パルスの立ち上がりの相対的な遅延は、"Write Calibration Register"コマンドをチップに送り、Calibration Register の値を書き換えることで変更できる。Calibration パルスの delay 値を 0 ns  $\sim 63$  ns の範囲で 1 ns 毎に変化させ、各 delay 値毎に Calibration パルスを入力した後にトリガーを送り、各チャンネルの検出効率を測定した。この測定では、第 3 章で説明したエッジ検出を'ON' に、ヒットの選択基準を"01X"に設定した。また Calibration パル

スの電荷量を 2 fC に、コンパレータの閾値を 0.5 fC にそれぞれ設定した。図 4.10 が SEABAS DAQ での測定結果であり、図 4.11 が SCT DAQ での測定結果である。各 delay 値に対してチップ単位の検出効率の変化が良い一致を示している。

図 4.10: Strobe delay 試験 (SEABAS DAQ)

ここで、次のゲインとノイズの測定で用いる Calibration パルスの delay 値を決めておく。以下の方法で、各チップの delay 値を決定した。Calibration パルスの delay は各チップ毎にしか設定できないので、128 チャンネルの検出効率からチップ単位の検出効率を求める。ある 1 つのチップの検出効率を delay の関数として描いたのが図 4.12 である。検出効率の立ち上がりと立ち下がりをそれぞれ誤差関数で fit し、検出効率が 50%となる delay time である  $t_{up}$  と  $t_{down}$  をそれぞれ求める。得られた  $t_{up}$  と  $t_{down}$  を用いて、

$$t_{up} + \frac{1}{4} \times (t_{down} - t_{up})$$

を delay の値とした [14]。

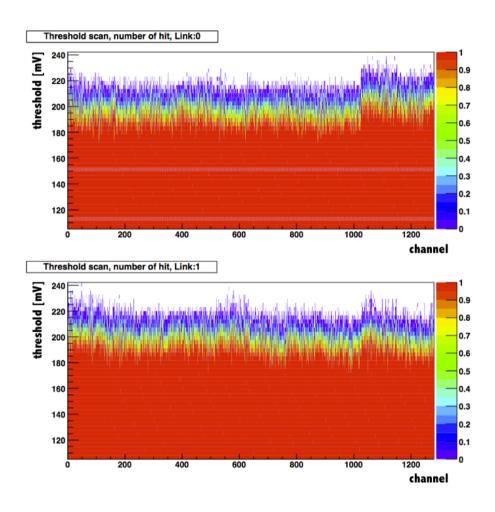

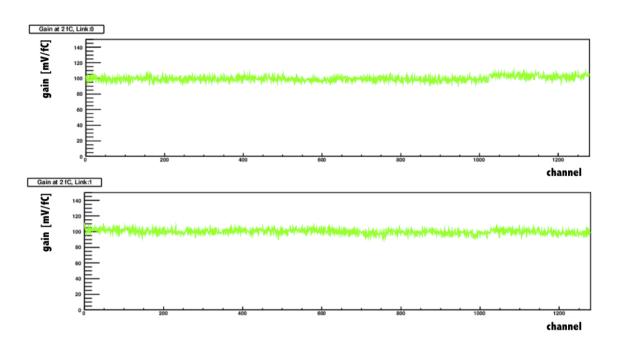

### ゲイン・ノイズ測定

ここでは SEABAS DAQ を用いて ABCN チップのゲインとノイズを測定し、その結果と SCT DAQ の測定結果を比較する。

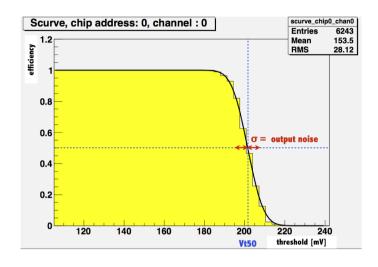

ABCN チップには ADC がないので、ゲインあるいはノイズを測定するには以下で示すように、検出効率あるいはノイズによるヒットの確率を閾値の関数として調べなければならない。Calibration パルスの電荷量を 2 fC に設定し、閾値を変化させ、各

図 4.11: Strobe delay 試験 (SCT DAQ)

図 4.12: Calibration パルス入力タイミングに対する検出効率の依存性

図 4.13: 閾値毎の各チャンネルの検出効率 (SEABAS DAQ)

閾値毎に検出効率を測定した結果を図4.13に示す。例としてチャンネル0の検出効率を閾値電圧の関数として描いたものが図4.14である。検出効率の立ち上がりを誤

図 4.14: チャンネル 0 における検出効率の閾値依存性 (SEABAS DAQ)

差関数で fit し、検出効率が 50%となる閾値電圧を求める。この閾値電圧を Vt50 と呼ぶ。また誤差関数の  $\sigma$  を出力ノイズとして評価する。ゲインは測定した Vt50 から

$$Gain[mV/fC] = \frac{Vt50[mV]}{q[fC]}$$

(4.1)

と求めることができる。ここで、q は Calibration パルスの電荷量である。ノイズは 測定した出力ノイズ $\sigma$ から

$$Noise[e] = \frac{\sigma[mV]}{Gain[mV/fC]} \cdot \frac{1}{1.6 \times 10^{-19}[C]}$$

(4.2)

と求めることができる。図 4.15 が SEABAS DAQ でのゲインの測定結果であり、図 4.16 が SCT DAQ での測定結果である。また図 4.17 が SEABAS DAQ でのノイズの 測定結果であり、図 4.18 が SCT DAQ での測定結果である。どちらの DAQ システムを使っても、ゲイン  $\simeq$ 100 mV/fC、ノイズ  $\simeq$ 400 e となり、2 つの DAQ システム による測定結果は一致している。

# 4.6 DAQ システムの動作確認に関するまとめと考察 <sub>まとめ</sub>

● 様々な動作確認の結果、SEABAS DAO が正しく動作している事を確認した。

図 4.15: SEABAS DAQ で測定した各チャンネルのゲイン [mV/fC] (上が link 0 で下が link 1)

図 4.16: SCT DAQ で測定した各チャンネルのゲイン [mV/fC] (上が link 0 で下が link 1)

図 4.17: SEABAS DAQ で測定した各チャンネルのノイズ [e] (上が link 0 で下が link 1)

図 4.18: SCT DAQ で測定した各チャンネルのノイズ [e] (上が link 0 で下が link 1)

- SCT DAQ では測定結果の図しか残せないが、SEABAS DAQ では図の他に生のデータも残せ、そのデータを用いて様々な解析が可能である。

- 1個の ABCN チップの読み出しではデータバスラインの本数が1本であったのに対し、20 個の ABCN チップの読み出しでは2本になった。ファームウェアの設計でデータバスライン毎に FIFO を用意することでこれに対応し、本研究のねらいのひとつであった複数個 (20 個)の ABCN チップの読み出しに成功した。またデータバスラインの本数を1本から2本へ拡張するのとは違い、2本からそれ以上の本数へ拡張することは容易である。よって、将来的に4個のモジュールを読み出すためにこのシステムを拡張することは容易であろう。

### 考察

- 今回、strobe delay 試験とゲイン・ノイズ測定の2つの測定結果をSEBAS DAQ と SCT DAQ で比較したが、ABCN チップの評価試験はこの2つ以外にもある。SEABAS DAQ にそれらの試験を組み込み、そこから得られた測定結果をSCT DAQの測定結果と比較した方がよい。

- 20個の ABCN チップを読み出せたが、最終的には4個以上のモジュール (ABCN チップ 320個以上に相当)を読み出さなければならない。そこで、SEABAS の容量と I/O 線の本数で読み出せるモジュール数を概算してみる。まず SEABAS の容量で4個以上のモジュールを読み出せるかを考える。1回の L1トリガーで 20個の ABCN チップから読み出されるデータ量は最大 ~3 kByte 程である。 SEABAS の User FPGA の容量は 162 kByte であるため、ABCN チップ ~1000個 (12個のモジュールに相当)までのデータを保持することができる。L1トリガー毎に読み出されたデータを PC に送るならば、SEABAS では4個以上のモジュールは十分に読み出せる。次に、SEABAS の I/O 線の本数で4モジュール以上を読み出せるかを考える。SEABAS には 120本の I/O 線が備わっており、4個のモジュールの読み出しに使う I/O 線の数は 38本であるため、SEABAS の I/O 線の本数で4個以上のモジュールは十分に読み出せる。以上より、SEABAS の仕様で4個以上のモジュールは読み出せるはずである。

# 第5章 プロトタイプ検出器の性能評価

開発した読み出しシステムを用いて、新型 SCT のためのプロトタイプ検出器の性能評価を行った。

図5.1にプロトタイプ検出器と信号読み出しのためのサブボードを示す。センサー

図 5.1: プロトタイプ検出器

図 5.2: センサー部の拡大図 (水色がチップ に接着されているセンサーであり、白色は チップに接着されていないセンサーである)

のサイズは  $9.75~\rm cm \times 9.75~cm$  でストリップ方向は  $2.4~\rm cm$  ごとの 4 つのセグメントに分かれている。今回使用したプロトタイプではノイズの静電容量依存性を調べるために図  $5.2~\rm o$ ようにそれぞれのチップに接続するセンサーの長さを変えてある。右側から chip 0, chip 1... と呼ぶことにすると、chip 0 と chip 1 に接続されたセンサー長は  $9.6~\rm cm$ 、chip 2 は  $7.2~\rm cm$ 、chip 3 は  $4.8~\rm cm$ 、chip 4 は  $2.4~\rm cm$  である。chip 5 以降はセンサーと接続されていない。センサーには合計  $1280~\rm cm$ ストリップがあり、そ

のストリップ間隔は 74.5  $\mu$ m である。センサーの主な仕様を表 5.1 にまとめる。今回 の測定で重要な静電容量は約 1.07 pF/cm である。

| センサーのタイプ                   | pバルク n <sup>+</sup> ストリップ               |

|----------------------------|-----------------------------------------|

| 抵抗                         | $\sim 6.7~\mathrm{k}\Omega\mathrm{cm}$  |

| サイズ                        | $9.75~\mathrm{cm}	imes9.75~\mathrm{cm}$ |

| 厚さ                         | $320~\mu\mathrm{m}$                     |

| ストリップピッチ                   | $74.5~\mu\mathrm{m}$                    |

| ストリップ幅                     | $16~\mu\mathrm{m}$                      |

| ストリップ数                     | 1280                                    |

| Interstrip Capacitance     | $\sim 0.8~\mathrm{pF/cm}$               |

| Body Capacitance per strip | $\sim 0.27~\mathrm{pF/cm}$              |

| 全空乏化電圧                     | 200 V                                   |

| 信号読み出し                     | ACカップリング                                |

|                            |                                         |

表 5.1: シリコンセンサーの主な仕様

## 5.1 ノイズ測定

第4章で述べ手順に従い、Calibration パルスの電荷量を 2 fC に設定し、ノイズを測定をした。測定は温度を 5 °C に保った恒温槽の中で行った。

### 5.1.1 バイアス電圧依存性

得られたノイズのバイアス電圧依存性を図 5.3 に示す。バイアス電圧が上がるに従いノイズが減少し、200 V に達した当たりからノイズが一定値になっていることがわかる。

上記のバイアス電圧依存性を理解するために、 $n^+$ ,  $p^+$  電極間の静電容量である Body Capacitance を考える。p-n 接合によってできる空乏領域では自由な電荷が存在しないので、空乏層は $n^+$ ,  $p^+$  電極間にコンデンサを形成する。Body Capacitance は、平行コンデンサを仮定すると、

$$C_{body} = \varepsilon \frac{S}{d} \tag{5.1}$$

で与えられる。ここで、 $\varepsilon$  は誘電率であり、S はセンサーの面積、d は空乏層の厚さである。式 (2.12) から空乏層の厚さはバイアス電圧と関係づけられている。バイア

ス電圧を上げることによって、空乏層は広がり、見かけの電極間距離が広くなる。その結果、Body Capacitance が小さくなる。一般にプリアンプのノイズは入力静電容量に依存しており、Body Capacitance が小さくなると、ノイズも減少する。バイアス電圧が全空乏化電圧である 200 V に達し全空乏化した後は、静電容量が一定になり、ノイズも一定値をとる。以上の考察により測定結果に見られるノイズのバイアス電圧依存性を理解できる。

# | Chip0 | Chip1 | Chip2 | Chip3 | Chip4 | Chip5

noise[ENC] vs bias voltage[V], cal charge: 2 fC

図 5.3: 逆バイアス電圧 [V] に対するノイズ [e] の変化 (chip 5 にはセンサーは接着されていない。)

100

150

bias voltage[V]

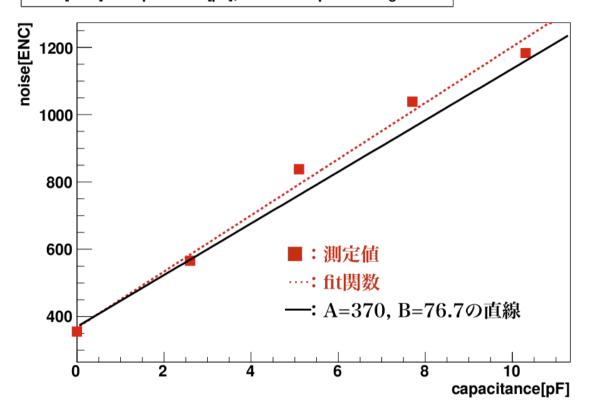

### 5.1.2 静電容量依存性

2000

1000

ノイズの静電容量依存性を評価するにあたり、まずセンサーの静電容量を見積もる。センサーへの静電容量の寄与は Body Capacitance の他に、近隣のストリップ間で形成される Interstrip Capacitance がある。Body Capacitance、Interstrip Capacitance ともに、表 5.1 で示したように、すでに測定されている [9]。センサー全体の静電容量を、Body Capacitance と Interstrip Capacitance の並列接続と考えると、それぞれのストリップの静電容量は 1.07 (=0.8+0.27) pF/cm となる。既に述べたように、そ

れぞれのチップに接着されているセンサーのストリップ長が異なるので、それぞれのチップに対する入力静電容量は表 5.2 に記された値となる。

表 5.2: 各チップに対する入力静電容量 [pF]

|        | 静電容量 [pF] |

|--------|-----------|

| chip 0 | 10.3      |

| chip 1 | 10.3      |

| chip 2 | 7.7       |

| chip 3 | 5.1       |

| chip 4 | 2.6       |

以上から、それぞれのチップへの入力静電容量が分かったので、前節の測定結果 (図 5.3) の全空乏化電圧 200 V における、各チップ毎のノイズを静電容量依存性に直して図示したのが図 5.4 である。静電容量の増加に従って、ノイズも増加している。一般にプリアンプからのノイズは、入力静電容量による寄与とアンプ自身のノイ

一般にプリアンプからのノイズは、入力静電容量による寄与とアンプ自身のノイズからなっており、入力静電容量 C[pF] の関数として、

$$Noise[e] = A + B \times C \tag{5.2}$$

で与えられる。ABCN チップの場合、

$$A[e] = 370$$

$$B[e/pF] = 76.7$$

とすでに測定されている [13]。式 (5.2) にこれらの値を代入した直線を図 5.4 に描いた。また測定値を一次関数で fit して得られる  $A_{\rm meas}$ ,  $B_{\rm meas}$  はそれぞれ、

$${\rm A_{meas}}[e] = 366.8 \pm 4.6$$

${\rm B_{meas}}[e/{\rm pF}] = 83.5 \pm 0.8$

と求められ、すでに測定されているA、Bと比較すると、近い値となった。

### noise[ENC] vs capacitance[pF], Calibration pulse charge : 2 fC

図 5.4: センサーの静電容量 [pF] に対するノイズ [e] の変化 (静電容量が 10.3 pF の時のノイズの値は chip 1 の方のノイズの値である)

### 5.2 宇宙線による検出器効率の測定

開発した読み出しシステムを用いて、プロトタイプ検出器の宇宙線に対する反応を調べた。SEABAS には NIM Input があり、それを用いる事により、外部トリガーでの読み出しを行った。測定は温度を 5 °C に保った恒温槽の中で行った。センサーにかける逆バイアス電圧は全空乏化電圧である 200 V に設定した。

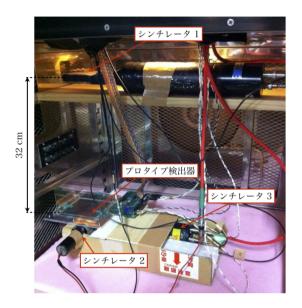

### 5.2.1 セットアップ

宇宙線測定のためのセットアップについて説明する。図 5.5 は恒温槽内部のプロトタイプ検出器とシンチレータの配置の様子である。トリガー用のシンチレータを3枚用意し、センサーの上に1枚、下に2枚配置する。シンチレータを上から順にシンチレータ1、シンチレータ2、シンチレータ3と呼ぶ。図 5.6 はセンサーと3枚のシンチレータの配置を上から見た概略図である。それぞれのシンチレータの面積は、シンチレータ1が7.0 cm×7.0 cm、シンチレータ2が4.5 cm×0.8 cm、シンチレータ3が5 cm×2.5 cm である。立体角をしぼるために、シンチレータ1をセンサーから32 cm 離して置いた。こうして配置した3枚のシンチレータのコインシデンスをとると、図 5.6 に示すように2.5 cm×0.8 cm の面積をカバーする事になる。このようにセットアップすることで、宇宙線が斜めに入射したとしても、chip 0と chip 2のセンサーがカバー面積の両サイドにあるので、検出できるはずである。各シンチレータに取り付けられている光電子増倍管に印加する電圧は宇宙線の信号が100 mV~200 mV 程度になるように設定した。

### 5.2.2 トリガー

トリガー用シンチレータからの出力に対し、discriminator によって 30 mV の閾値を設定し (出力は 100 ns 幅)、3 つのシンチレータのヒットのコインシデンスをトリガーとした。シンチレータ 2 は面積が小さいため、信号のタイミングが宇宙線の通過した位置にあまり依らない。そこでシンチレータ 2 の信号のタイミングでトリガー信号を発行するために、シンチレータ 2 の信号だけコインシデンスに入る前に遅延回路を通して 40 ns 遅延させた。こうして作られたトリガー信号を SEABAS の NIM Input に入力すると、SEABAS が L1 トリガーをチップに送る。

各シンチレータのシングルレートを表 5.3 にまとめる。ここからアクシデンタルレートは $\sim 6.9 \times 10^{-14}$  Hz と求められる。3 つのコインシデンスレートは $\sim 0.0013$  Hz であり、アクシデンタルレートは無視できる。

図 5.5: 恒温槽内部のプロトタイプ検出器 と 3 枚のシンチレータの配置の様子

図 5.6: センサーと 3 枚のシンチレータの 配置を上から見た概略図

表 5.3: 3つのシンチレータのシングルレート

|          | シングルレート [Hz] |

|----------|--------------|

| シンチレータ1  | ~6.9         |

| シンチレータ 2 | ~0.43        |

| シンチレータ3  | ~3.85        |

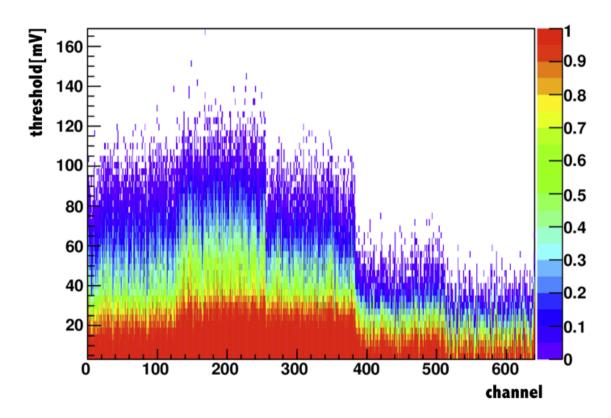

### 5.2.3 閾値の設定

図5.4から分かるようにチップに接続されたセンサーの長さが違うためにチップ毎にノイズが違う。そのためノイズの量に応じた閾値を各チップに設定する必要がある。そこで本節では各チップに対する閾値の設定方法を説明する。

まず、各チャンネルのノイズが閾値を超える確率を測定した。これを閾値を変化させ繰り返した結果を図 5.7 に示す。この結果から、Vt50 [mv] と出力ノイズ  $\sigma$  [mV] を

図 5.7: 各チャンネルのノイズが閾値を越える確率

第 4 章で述べた手順で求める。各チップで得られた Vt50~[mV] と出力ノイズ  $\sigma~[mV]$  を表 5.4~ にまとめる。

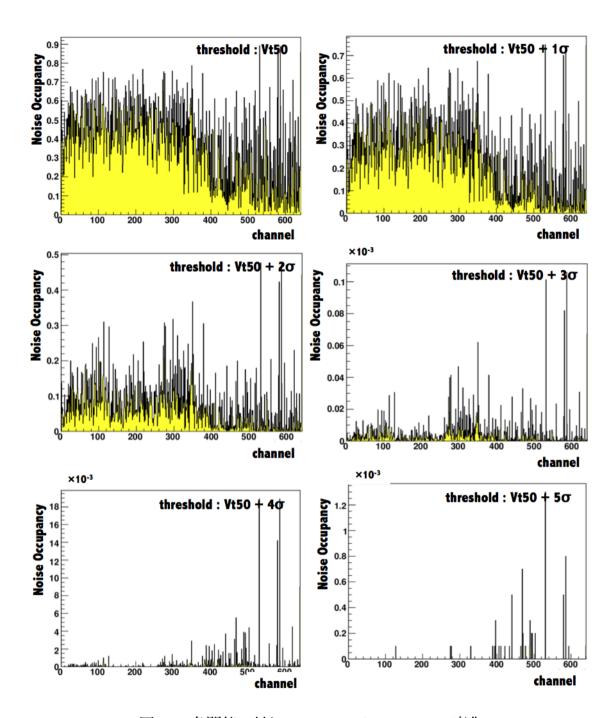

次に各チップに設定する閾値を Vt50, Vt50+ $\sigma$ , Vt50+ $2\sigma$ , Vt50+ $3\sigma$ , Vt50+ $4\sigma$ , Vt50+ $5\sigma$  と変化させ、それぞれの閾値でランダムトリガーを 10,000 回ずつチップに送った。その結果から、以下で定義するノイズによる Occupnacy (Noise Occupancy) を各チャンネル毎に求めた。

Noise Occupancy =

$$\frac{N_{hits}}{N_{events}}$$

(5.3)

ここで、 $N_{hits}$  は閾値を越えた回数であり、 $N_{events}$  はイベント数 (=10,000) である。各閾値での測定結果を図 5.8 に示す。プロトタイプ検出器の検出効率を O(0.1~%) 程

表 5.4: 各チップのセンサーの Vt50[mV] と出力ノイズ σ[mV]

|        | Vt50[mV] | 出力ノイズ $\sigma[mV]$ |

|--------|----------|--------------------|

| chip 0 | 39.2     | 20.1               |

| chip 1 | 55.0     | 24.9               |

| chip 2 | 42.5     | 16.7               |

| chip 3 | 25.3     | 8.8                |

| chip 4 | 19.3     | 4.8                |

度の精度で求めるために、すべてのストリップで Noise Occupancy が  $10^{-3}$  以下になる  $Vt50+5\sigma$  を各チップの閾値として設定する。

次に、設定した閾値で Minimum Ionizing Particle (MIP) の信号が見えるかを考える。シリコンセンサーに MIP が垂直入射した時、 $1\mu$ m 当たり約 80 個の電子正孔対が生じる。プロトタイプ検出器のシリコンセンサーの厚さは  $320\mu$ m であることから、MIP がセンサーを通過した時、 $2.6\times10^4~e~(\sim4~fC)$  に相当する信号が生じる (ただし電荷収集率は 1 ではない)。そこで Calibration パルスの電荷量を 3~fC あるいは 4~fC に設定して、各ストリップの検出効率を閾値を変化させながら測定する。その測定結果を図 5.9 に示す。図からわかるように  $Vt50+5\sigma$  の閾値では、すべてのストリップで検出効率が 1 である。よって、 $Vt50+5\sigma$  の値を閾値として以下の測定を行う。

### 5.2.4 タイミング調整

宇宙線が入射した時に収集したデータを読み出すためにトリガーのタイミングを調整する必要がある。ここでは、そのタイミングをまず L1 delay time で調整し、その後 cable delay で微調整した。3つのシンチレータのコインシデンスをトリガー信号に用いるとレートが $\sim$ 0.0013 Hz と低いため、以下の測定では、シンチレータ 2 とシンチレータ 3 のコインシデンスをトリガー信号に用いる。この時のレートは $\sim$ 0.028 Hz である。

まず、L1 delay time を設定する方法を述べる。3章で説明したように、センサーに 荷電粒子が通過すると、そのヒット情報は ABCN チップ内の Pipeline に保持される。その後、L1 トリガー信号を受けると、前もって指定された L1 delay time 前のイベントとその前後のイベントの合計 3イベント分のヒットデータが読み出される。L1 delay time は、"Write L1 Delay Register"コマンドを送り、チップ内部の"L1 Delay Register"の値を書き換えることにより、変更できる。

読み出されるヒットパターンの 3bit はそれぞれ、

XXX: Previous event, Current event, Next event

図 5.8: 各閾値に対しての Noise Occupancy の変化

図 5.9: 各閾値毎の各ストリップの検出効率 (実線は各チップに設定した閾値  $(Vt50+5\sigma)$ )

に対応しており、Current event の bit に宇宙線によるヒットがくるように L1 delay time を調整する。

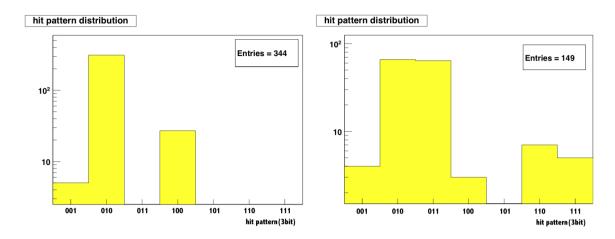

L1 delay time の値を決めた後、SEABAS の NIM Input へのトリガー信号用ケーブルの長さを変える事で、トリガー信号がチップに入るタイミングを微調整する。ケーブルの微調整前では、3章で説明したエッジ検出"ON"での測定ではヒットパターン'001'が存在しなかったが、ケーブルの長さを次第に長くすることによって、'001'のヒットパターンが出現しはじめた。その時のケーブルの長さを cable delay として設定した。調整後のエッジ検出"ON"で測定したヒットパターンの分布を図 5.11 に示す。より詳細なヒットパターンをみるためにエッジ検出"OFF"にしての測定も行った。その時のヒットパターンをみるためにエッジ検出"OFF"の測定で、149イベント中138イベントがヒットパターンが'X1X'(ここで X は'0' か'1' のどちらか)のイベントであった。これより全体の 93 %のイベントで、宇宙線によるヒットが Current event の bit にあることが分かる。

### 5.2.5 検出効率測定

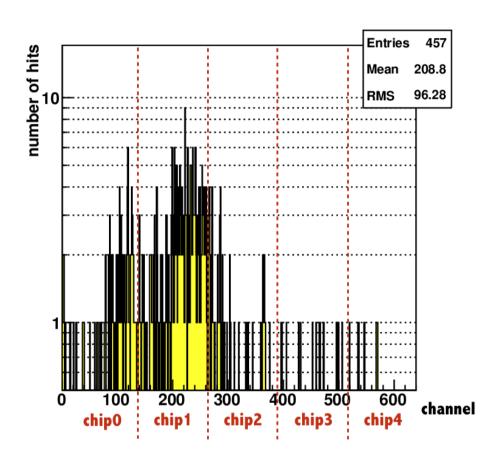

ここではプロトタイプ検出器の宇宙線に対する検出効率を見積もる。トリガーしたイベント数は360イベントで、そのうちセンサーに1つ以上のヒットがあったイベントは328イベントであった。これからプロトタイプ検出器の検出効率は91.1±1.5%と求めれる。これは一般的な半導体検出器の検出効率 >99%に比べると非常に低い検出効率である。

より詳細に調べるために、ヒットがあったイベントのストリップ分布を図 5.12 に示す。図から 3 枚のシンチレータのコインシデンスによりカバーされる領域がある chip 1 以外のチップにもヒットがある事が分かる。chip 3 にも ~10 程のヒットがあ

図 5.10: エッジ検出"ON"の時のヒットパ 図 5.11: エッジ検出"OFF"の時のヒットパ ターン (XXX: Previous, Current, Next) ターン (XXX: Previous, Current, Next)

ることから、 $chip\ 0$  の隣のセンサーの無い領域 (以下、領域 I と呼ぶ。) にも  $\sim 10$  個程度の宇宙線が入射した可能性がある。以下でこの数を簡単に見積もり、この補正をかけた検出効率を求める。

${

m chip}\ 0$  のヒット数を  ${

m N}_0$ 、 ${

m chip}\ 2$  のヒット数を  ${

m N}_2$ 、 ${

m chip}\ 3$  のヒット数を  ${

m N}_3$ 、 ${

m chip}\ 4$  のヒット数を  ${

m N}_4$  とすると、領域  ${

m I}$  への入射粒子数  ${

m N}_I$  は

$$N_I = \frac{N_0}{N_2} \times (N_3 + N_4)$$

と考えられる。測定結果  $N_0$ =98、 $N_2$ =78、 $N_3$ =15、 $N_4$ =7を使うと、 $N_I$ =27となる。この補正を加えると検出効率は 98.5±0.64% となる。ただし、上記の補正は斜め入射を仮定しており、その系統誤差の評価には至っていない。

そこで、検出効率をより精度よく求めるためには、

- 宇宙線の斜め入射をなくすために、1 cm 角程のサイズの小さいシンチレータを2枚用意し、それのコインシデンスで測定する。

- 宇宙線が入射した位置を  $O(\sim 1 \text{ mm})$  の精度で特定できる参照用検出器を用いて、測定する。

ことなどが考えられる。

図 5.12: ヒットがあったイベントのストリップ分布

# 第6章 まとめと考察

### • 試験用読み出しシステムの開発

### - まとめ

読み出しの対象である ABCN チップの理解からはじまり、チップの初期 化、Calibraion パルスの入射テストなどの過程を経て、1 個の ABCN チップの読み出しシステムの構築までに至った。そこから 20 個の ABCN チップの読み出しシステムへ発展させ、その開発した読み出しシステムを用いて ABCN チップ 20 個が搭載されたフレックスハイブリッド基板の性能評価試験を行った。そこで得られた結果は既存の読み出しシステムの結果と良い一致を示し、開発した読み出しシステムが正しく動作していることを確認できた。

### - 考察・課題

今回 20 個の ABCN チップの読み出しは達成できたが、最終的には 4 個以上のモジュール (ABCN チップ 320 個に相当) の読み出しをしなければならない。4章に示したように SEABAS の仕様で 4 個以上のモジュールの読み出しは可能なはずである。今後、実際にどれだけの ABCN チップを SEABAS を用いた読み出しシステムで読み出すことができるかを調べる必要がある。

### • プロトタイプ検出器の性能評価

### - まとめ

プロトタイプ検出器のノイズのバイアス電圧依存性と静電容量依存性を測定した。測定値からプリアンプのノイズを入力静電容量 C[pF] の関数で、Noise $[e]=(366.8\pm4.6)+(83.5\pm0.8)\times C$  と求めた。また宇宙線を用いて、プロトタイプ検出器の検出効率を  $91.1\pm1.5\%$  と求めた。

### - 考察・課題

測定したノイズは事前に測定されていた値と近い値になった。よって、開発した読み出しシステムを用いると、チップの性能評価試験だけではなく、検出器のノイズの定量的な評価もできることが確認できた。測定結果のノイズの原因などの考察までには至っていない。またノイズの温度依存

性、リーク電流との相関などを調べることは検出器の放射線耐性を評価するのに、重要である。これらの試験も今後必要である。

測定した検出効率は、一般的な半導体検出器の検出効率と比べると十分なものではなかった。その原因が宇宙線の斜め入射であると推測し、補正を加えたところ、検出効率は誤差の範囲で99%になった。よって、開発した読み出しシステムを用いると、外部トリガーで宇宙線からの信号を正しいタイミングで読み出せることが確認できた。補正した検出効率はある仮定に基づいているため、評価できていない系統誤差がある。よって、そのような仮定なしに検出効率をより精度よく測定するには、斜め入射の宇宙線をなくすために、小さいシンチレータのコインシデンスで測定するなどの測定方法が考えられる。

# 第7章 結論

本研究では、新型SCT用のプロトタイプ検出器を試験するための読み出しシステムを開発し、様々な動作確認の結果、システムが正しく動作していることを確認できた。SEABASには大容量のFPGAと120本のI/O線が搭載されており、仕様では4個のモジュールの読み出しが可能である。また本研究では複数個のABCNチップの読み出しにも成功した。4章で述べたように、このシステムを4個のモジュールの読み出しに拡張することに技術的な障壁はない。よって、将来的にこの開発したシステムで4個のモジュールの読み出しは可能なはずである。また開発した読み出しシステムを用いると、チップの性能評価試験だけではなく、プロトタイプ検出器のノイズの定量的な評価や宇宙線に対する検出効率の測定ができることを示した。開発した読み出しシステムは狙い通り、汎用性・利便性の高いものである。

# 付 録 A ABCN チップ

### A.1 データフォーマット

"Master"として初期化された ABCN チップが出力するパケットは次の3つの要素に分ける事ができる。

- "Master"チップによって生成された 13-bit の"header"

- "Master"チップを含む daisy-chain 接続されたすべてのチップからの一連のデータパケット

- Daisy-chainの最下流に位置する"End"チップによって送られてくる17-bitの"trailer"

表 A.1 にデータパケットのフォーマットを示す。

表 A.1: データフォーマット

| Preamble | DT | LVL1 | BC       | Sep | Data                | Data | Data                | Trailer     |

|----------|----|------|----------|-----|---------------------|------|---------------------|-------------|

| 11101    | 0  | nnnn | bbbbbbbb | 1   | <block_1></block_1> |      | <blook_n></blook_n> | 1000 0000   |

|          |    |      |          |     |                     |      |                     | 0000 0000 0 |

- DT (Data Type)

ABCN チップの場合、DT は常に'0' である。

- Level 1

"Soft Reset"コマンドから現在までにきた"L1 Trigger"の回数。

- Bunch Crossing Number

"Soft Reset"コマンドまたは"BC Reset"コマンドから現在までのビーム衝突の

回数。

### • Data Block

"Master"チップを含むすべてのチップから出力されるデータの本体。データブロックは、"Physics Data", "No Hit Data", "Configuration Data", "Error Data" のいずれかのタイプに分類できる。

Data Block の4つのタイプの詳細について以下で説明する。

### **Physics Data**

このデータパケットは検出器からのヒット情報が記述されている。このデータは 1つ以上のデータパケットで構成される。表 A.2 に"Physics Data"のフォーマットを 示す。このデータパケットには"Isolated Hit Data Packet"と"Non Isolated Hit Data Packet"の 2 つのタイプがある。"Physics Data"はこの 2 つのタイプのパケットの組 み合わせから構成される。

表 A.2: ヒットデータフォーマット

| Data Packet         | Data Packet         | Data PAcket         | Data Packet         |

|---------------------|---------------------|---------------------|---------------------|

| <block_1></block_1> | <block_2></block_2> | <block_i></block_i> | <block_n></block_n> |

### • Isolated Hit Data Packet

このパケットは、隣接するチャンネルにヒットがない時に、ヒットチャンネルからのデータを送るために使われる。表 A.3 が"Isolated hit data packet"である。

表 A.3: Isolated ヒットデータパケット

| Isolated Hit Data Packet |                                                    |       |   |     |  |  |

|--------------------------|----------------------------------------------------|-------|---|-----|--|--|

| Header                   | Chip Address   Channel Address   Sep   Hit Pattern |       |   |     |  |  |

| 1                        | aaaaaaa                                            | ccccc | 1 | ddd |  |  |

ヒットパターン (3bit) はそれぞれ、"Previous", "Current", "Next"のヒットに対応する。

### • Non Isolated Hit Data Packet

このパケットは、2つ以上の隣接するチャンネルにヒットがある時、それらのデータをグループ化して送るために使われる。データパケットには、チップアドレスとグループの最初のチャンネルアドレスがあり、その後に各ヒットチャンネルのデータが続く。表 A.4 が"Non Isolated hit data packet"である。

表 A.4: Non Isolated ヒットデータパケット

| Non Isolated Hit Data Packet |         |                                                                |   |         |   |         |   |          |

|------------------------------|---------|----------------------------------------------------------------|---|---------|---|---------|---|----------|

| Header                       | Chip    | Chip First Hit Channel Sep First Hit Sep Next Hit Sep Last Hit |   |         |   |         |   | Last Hit |

|                              | Address | Address                                                        |   | Pattern |   | Pattern |   | Pattern  |

| 1                            | aaaaaaa | ccccc                                                          | 1 | ddd     | 1 | ddd     | 1 | ddd      |

### No Hit Data

イベントにヒットしたチャンネルひとつも無ければ、チップは"No Hit Data Packet" を出力する。表 A.5 が"No Hit Data Packet"である。

表 A.5: No Hit データパケット

| Data Packet |

|-------------|

| 0011        |

### Configuration Data

"Configuration Data"は、チップが"Send\_ID Mode"または"Read Register Mode"である時のL1トリガーに対するレスポンスとして出力される。チップが"Send\_ID Mode"の時と"Read Register Mode"の時では"Configuration Data"は異なるデータフォーマットになっている。

"Send\_ID Mod"の時 データのパケットには、チップアドレスの他に"Configuration Register 1"の内 容を含んでいる。表 A.6 に"Configuration Data Packet"を示す。

表 A.6: Configuration データパケット

| Configuration Data Packet |                                       |                                          |  |  |  |  |

|---------------------------|---------------------------------------|------------------------------------------|--|--|--|--|

| Header                    | Chip                                  | Chip Sep MSB Byte of Sep LSB Byte of Sep |  |  |  |  |

|                           | Address Config Pattern Config Pattern |                                          |  |  |  |  |

| 000                       | aaaaaaa                               |                                          |  |  |  |  |

"Read Register Mode"の時 データのパケットには、チップアドレスの他にレジスタアドレスとレジスタの内 容が含まれている。表 A.7 に"Register Data Packet"、表 A.8 に"Read Register Address"をそれぞれ示す。

表 A.7: Register データパケット

|        | Register Data Packet |                                                   |         |               |   |               |     |

|--------|----------------------|---------------------------------------------------|---------|---------------|---|---------------|-----|

| Header | Chip                 | Chip Sep Register MSB Byte of Sep LSB Byte of Sep |         |               |   |               | Sep |

|        | Address              |                                                   | Address | Register Data |   | Register Data |     |

| 000    | aaaaaaa              | 010                                               | rrrrr   | ddddddd       | 1 | ddddddd       | 1   |

表 A.8: Read Register アドレス

| rrrrr  |                          |

|--------|--------------------------|

| 000 00 | Configuration Regster 1  |

| 001 00 | Mask Register            |

| 010 00 | Calibration Register     |

| 011 10 | Fuse Register            |

| 011 00 | Threshold Register       |

| 111 00 | Bias Register 1          |

| 111 01 | Bias Register 2          |

| 111 10 | Bias Register 3          |

| 000 10 | TrimDac                  |

| 001 10 | Configuration Register 2 |

| 010 10 | L1 Delay Register        |

| 101 10 | Status Register 1        |

| 110 10 | Status Register 2        |

### **Error Data**

チップがエラーを検出すると"Error Data"が送られてくる。表 A.9 に"Error Data Format"を示す。

エラーコードには2種類あり、

表 A.9: Error データフォーマット

| Error Data Packet |              |            |     |

|-------------------|--------------|------------|-----|

| Header            | Chip Address | Error Code | Sep |

| 000               | aaaaaaa      | eee        | 1   |

- eee = 001 の時、"No Data Available"

- eee = 100の時、"Buffer Overflow"

をそれぞれあらわす。

# 謝辞

本論文を終わるにあたって、この2年の間にお世話になった方々に、お礼を述べて いきたいと思います。

研究を進める上で助言とご指導を下さった花垣和則准教授には心から感謝しております。この2年間、多くの研究の機会を与えて下さり、素晴らしい研究生活を送ることができました。この修士論文が、人様に見せられるような文章になったのも花垣さんの添削のおかげです。本当にありがとうございました。

素晴らしい研究環境を与えてくださった山中卓教授に深く感謝しております。その鋭い洞察力での指摘は普段見落としがちな事柄を的確に指し示すものであり、多くを学ばせていただきました。本当にありがとうございました。

KEKの海野義信さん、池上陽一さんには KEK での素晴らしい研究環境を与えて下さったことに感謝しております。私の様々な質問に答えて下さったことも、深く感謝しております。ありがとうございました。

阪大ATLASグループの先輩である廣瀬穣さん、目黒立真さん、元阪大ATLASグループの内田桐日さん、高木崇志さんには研究に関して多くのことを教えて下さったことに感謝しております。同期の内田潤くんとはお互いの研究の苦労話から世間話まで言い合えることができ、楽しい研究生活を送ることができました。本当にありがとう。後輩であり本研究の共同実験者である遠藤理樹くんには、研究に関して多くの助力をいただきました。この研究がここまで到達できたのも遠藤くんの助力があったからこそです。感謝しております。

助教の外川学さん、先輩の岩井瑛人さん、中谷洋一さん、柳田陽子さん、同期の杉山泰之くんには、私の狭かった世界を広げて下さったことに深く感謝しております。与えてくださった多く知識は、私の人生にパラダイムシフトを引き起こしたといっても過言ではないと思います。本当にありがとうございました。特任研究員の李栄篤さん、先輩の佐藤和史さん、Lee Jong-won さん、村山理恵さんには様々な知識を与えて下さったことに感謝しております。特に李栄篤さんと Lee Jong-won さんには、私の博士後期課程進学への期待や不安について相談にのっていただいたことにも深く感謝しております。私が進学を決意できたこともお二方の存在が大きかったです。ありがとうございました。後輩の宇井利昌くん、鎌倉恵太くん、伴野真太郎くん、東野聡くんにはいつも私の無茶なフリや他愛もない話に付きあっていただいたことに感謝しております。秘書の亀井彰子さんには事務的な手続きではいつもお世話になりました。感謝しております。

# 参考文献

- [1] ATLAS Collaboration, ATLAS Detector and Physics Performance Technical Design Report Volume I, ATLAS TDR 14, CERN/LHCC 99-14 (1999).

- [2] ATLAS Collaboration, ATLAS Detector and Physics Performance Technical Design Report Volume II, ATLAS TDR 15, CERN/LHCC 99-15 (1999).

- [3] F. Campabadal, et al. Design and performance of the ABCD3TA ASIC for readout of silicon strip detectors in the ATLAS semiconductor tracker, Nucl. Instr. and Meth. A 552 (2005) 292-328.

- [4] Y.Unno, Silicon sensor development for the ATLAS upgrade for SLHC, Nucl. Instr. and Meth. A 569 (2006) 41-47.

- [5] D.Pitzl, et al. Type inversion in silicon detector, Nucl. Instr. and Meth. A 311 (1992) 98-104.

- [6] G.Lindström, Radiation damage in silicon detectors, Nucl. Instr. and Meth. A 512 (2003) 30-43.

- [7] Tomohisa Uchida, "Hardware-Based TCP Processor for Gigabit Ethernet," IEEE Transactions on Nuclear Science, 55, pp.1631-1637 (2008).

- [8] Tomohisa Uchida and Yasuo Arai, SEABAS (Soi EvAluation BoArd with Sitcp) User's Manual

- [9] J. Bohm, et al. Evaluation of the bulk and strip characteristics of large area n-in-p silicon sensors intended for a very high radiation environment, Nucl. Instr. and Meth., A (2010).

- [10] Y.Unno, et al. Development of n-on-p silicon sensors for very high radiation environments, Nucl. Instr. and Meth., A (2010).

- [11] ABC-N ASIC Specifications Version V1.3.1, (2008).

- [12] J.Kaplon, et al. The ABCN front-end chip for ATLAS Inner Detector Upgrade.

- [13] F.Anghinolfi, et al. Performance of the ABCN-25 readout chip for the ATLAS Inner Detector Upgrade.

- [14] P.W.Phillips and L.Eklund, Electrical Tests of SCT Hybrids and Modules.

- [15] W.R.Leo, Techniques for Nuclear and Particle Physics Experiment, Spring-Verlag(1987).

- [16] G.F.Knoll, Radiation Detection and Measurement, Wiley(2000).